Southern Illinois University Carbondale

OpenSIUC

Dissertations

Theses and Dissertations

5-1-2024

# Resource Optimized Scheduling For Enhanced Power Efficiency And Throughput On Chip Multi Processor Platforms

Shivam Kundan Southern Illinois University Carbondale, shivamkundan@hotmail.com

Follow this and additional works at: https://opensiuc.lib.siu.edu/dissertations

### **Recommended Citation**

Kundan, Shivam, "Resource Optimized Scheduling For Enhanced Power Efficiency And Throughput On Chip Multi Processor Platforms" (2024). *Dissertations*. 2214. https://opensiuc.lib.siu.edu/dissertations/2214

This Open Access Dissertation is brought to you for free and open access by the Theses and Dissertations at OpenSIUC. It has been accepted for inclusion in Dissertations by an authorized administrator of OpenSIUC. For more information, please contact opensiuc@lib.siu.edu.

# RESOURCE-OPTIMIZED SCHEDULING FOR ENHANCED POWER EFFICIENCY AND THROUGHPUT ON CHIP MULTI-PROCESSOR PLATFORMS

by

Shivam Kundan

M.S., Southern Illinois University Carbondale, 2019

A Thesis Submitted in Partial Fulfillment of the Requirements for the Doctor of Philosophy Degree

School of Electrical, Computer, and Biomedical Engineering in the Graduate School Southern Illinois University Carbondale May 2024 Copyright by Shivam Kundan, 2024 All Rights Reserved

### DISSERTATION APPROVAL

# RESOURCE-OPTIMIZED SCHEDULING FOR ENHANCED POWER EFFICIENCY AND THROUGHPUT ON CHIP MULTI-PROCESSOR PLATFORMS

by

Shivam Kundan

A Thesis Submitted in Partial

Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

in the field of Electrical and Computer Engineering

Approved by:

Dr. Iraklis Anagnostopoulos, Chair

Dr. Dimitri Kagaris, Co-Chair

Dr. Spyros Tragoudas

Dr. Chao Lu

Dr. Khaled Ahmed

Graduate School Southern Illinois University Carbondale April 9, 2024

### AN ABSTRACT OF THE THESIS OF

Shivam Kundan, for the Doctor of Philosophy degree in ELECTRICAL AND COMPUTER ENGINEERING, presented on April 9, 2024, at Southern Illinois University Carbondale. TITLE: RESOURCE-OPTIMIZED SCHEDULING FOR ENHANCED POWER EFFICIENCY AND THROUGHPUT ON CHIP MULTI-PROCESSOR PLATFORMS

#### MAJOR PROFESSOR: Dr. I. Anagnostopoulos

The parallel nature of process execution on Chip Multi-Processors (CMPs) has boosted levels of application performance far beyond the capabilities of erstwhile single-core designs. Generally, CMPs offer improved performance by integrating multiple simpler *cores* onto a single die that share certain computing resources among them such as last-level caches, data buses, and main memory. This ensures architectural simplicity while also boosting performance for multi-threaded applications. However, a major trade-off associated with this approach is that concurrently executing applications incur performance degradation if their collective resource requirements exceed the total amount of resources available to the system. If dynamic resource allocation is not carefully considered, the potential performance gain from having multiple cores may be outweighed by the losses due to contention for allocation of shared resources. Additionally, CMPs with inbuilt dynamic voltage-frequency scaling (DVFS) mechanisms may try to compensate for the performance bottleneck by scaling to higher clock frequencies. For performance degradation due to shared-resource contention, this does not necessarily improve performance but does ensure a significant penalty on power consumption due to the quadratic relation of electrical power and voltage  $(P_{dynamic} \propto V^2 \cdot f)$ .

This dissertation presents novel methodologies for balancing the competing requirements of high performance, fairness of execution, and enforcement of priority, while also ensuring overall power efficiency of CMPs. Specifically, we (1) Analyze the problem of

i

resource interference during concurrent process execution and propose two fine-grained scheduling methodologies for improving overall performance and fairness, (2) Develop an approach for enforcement of priority (i.e., minimum performance) for specific processes while avoiding resource starvation for others, and (3) Present a machine-learning approach for maximizing the power efficiency (performance-per-Watt) of CMPs through estimation of a workload's performance and power consumption limits at different clock frequencies.

As modern computing workloads become increasingly dynamic, and computers themselves become increasingly ubiquitous, the problem of finding the ideal balance between performance and power consumption of CMPs is of particular relevance today, especially given the unprecedented proliferation of embedded devices for use in Internet-of-Things, edge computing, smart wearables, and even exotic experiments such as space probes comprised entirely of a CMP, sensors, and an antenna ("space chips"). Additionally, reducing power consumption while maintaining constant performance can contribute to addressing the growing problem of dark silicon.

### DEDICATION

To my father, who inspired and enabled my life-long dream of pursuing engineering. To my mother, who has always supported and encouraged my academic pursuits through all the many ups and downs. To my sister, who has always been a source of support and amusing mischief. To my late grandfather, who encouraged me to always dream big and boldly follow my passions. To my grandmother, who has always had unshakeable belief in me. To my aunt, who has been a role-model for reasons both academic and more. Finally, to my cat Data, who has been a constant source of companionship, happiness, and delight throughout my college education.

### ACKNOWLEDGMENTS

I would like to thank Dr. Iraklis Anagnostopoulos for his invaluable assistance, guidance, and tremendous patience all throughout my undergraduate and graduate study, and for encouraging me to purse a PhD. I would also like to thank Dr. Spyros Tragoudas who was the one to first suggest pursuing a graduate education. I would like to thank my committee co-chair Dr. Dimitri Kagaris for inspiring my interest in the field, through his excellent teaching in the many undergraduate and graduate courses I took under him. I would also like to thank Dr. Chao Lu and Dr. Khaled Ahmed for taking the time to be part of my dissertation committee. Finally, a sincere thank you to my fellow PhD students Theodoros Marinakis, Ioannis Galanis, Zois Tasoulas, and Ourania Spantidi for their constant help and support in both classwork and research.

## TABLE OF CONTENTS

| CHAPTER                                               | PAGE   |

|-------------------------------------------------------|--------|

| ABSTRACT                                              | . i    |

| DEDICATION                                            | . iii  |

| ACKNOWLEDGMENTS                                       | . iv   |

| LIST OF TABLES                                        | . ix   |

| LIST OF FIGURES                                       | . X    |

| LIST OF ALGORITHMS                                    | . xiii |

| CHAPTERS                                              |        |

| 1: Introduction                                       | . 1    |

| 1.1: Decline of Single-Core Architectures             | . 1    |

| 1.2: Chip Multi Processors                            | . 2    |

| 1.3: Chip Multi Processor Challenges                  | . 4    |

| 1.4: Conclusion                                       | . 5    |

| 1.5: Research Questions                               | . 5    |

| 1.6: Contributions                                    | . 6    |

| 2: Literature Review                                  | . 8    |

| 2.1: Contention-Aware Scheduling                      | . 8    |

| 2.2: Power-Aware Scheduling                           | . 11   |

| 3: Contention-Aware Scheduling                        | . 17   |

| 3.1: Shared-Resource Contention                       | . 17   |

| 3.2: Motivation: The effect of finer-grain scheduling | . 21   |

| 3.3: Pro     | posed Methodology                                    | 23 |

|--------------|------------------------------------------------------|----|

| 3.3.1        | Application Characterization & Interference Analysis | 24 |

| 3.3.2        | Static Pressure-Aware Scheduling Policy              | 31 |

| 3.3.3        | Dynamic Pressure-Aware Scheduling Policy             | 35 |

| 3.4: Exp     | perimental Results                                   | 40 |

| 3.4.1        | Experimental setup                                   | 40 |

| 3.4.2        | Single-Threaded Workload Performance                 | 44 |

| 3.4.3        | Multi-Threaded Workload Performance                  | 50 |

| 3.4.4        | Enabling hyper-threading                             | 52 |

| 3.4.5        | Performance of Dynamic vs. Static Scheduling Policy  | 53 |

| 3.5: Con     | clusion                                              | 55 |

| 4: Priority- | Aware Scheduling                                     | 56 |

| 4.1: Intr    | oduction                                             | 56 |

| 4.2: Pro     | posed Methodology                                    | 58 |

| 4.2.1        | Application Characterization                         | 58 |

| 4.2.2        | Progress                                             | 59 |

| 4.2.3        | Priority                                             | 59 |

| 4.2.4        | Application-to-Core Assignment                       | 60 |

| 4.3: Eva     | luation Setup                                        | 64 |

| 4.4: Exp     | erimental Results                                    | 65 |

| 4.4.1        | High Priority Application Performance                | 65 |

| 4.4.2        | Overall Workload Performance                         | 68 |

| 4.4.3        | Overhead                                             | 69 |

| 4.5: Con     | clusion                                              | 69 |

| 5: | Power-A    | ware Scheduling                           | 71 |

|----|------------|-------------------------------------------|----|

|    | 5.1: Intro | oduction                                  | 71 |

|    | 5.2: Mot   | ivation                                   | 72 |

|    | 5.3: Prop  | posed Methodology                         | 73 |

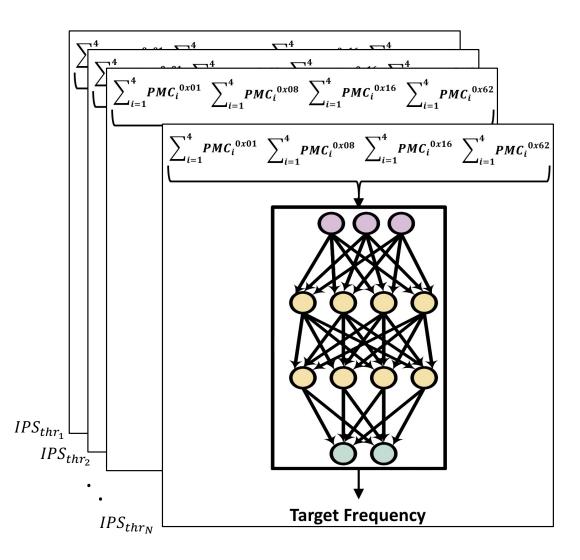

|    | 5.3.1      | Selection of PMC events                   | 74 |

|    | 5.3.2      | Training of MLPs                          | 75 |

|    | 5.3.3      | Run-Time Frequency Selection              | 77 |

|    | 5.3.4      | Comparison of classification approaches   | 77 |

|    | 5.4: Eval  | uation                                    | 78 |

|    | 5.5: Con   | clusion                                   | 81 |

| 6: | Performa   | nce & Power Aware Scheduling              | 83 |

|    | 6.1: Intro | oduction                                  | 83 |

|    | 6.2: Prop  | posed Methodology                         | 84 |

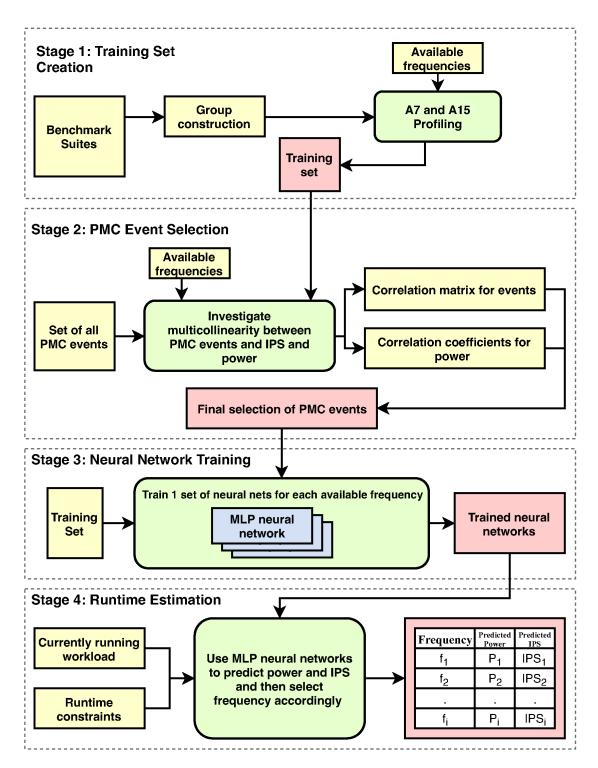

|    | 6.2.1      | Training Set Creation                     | 84 |

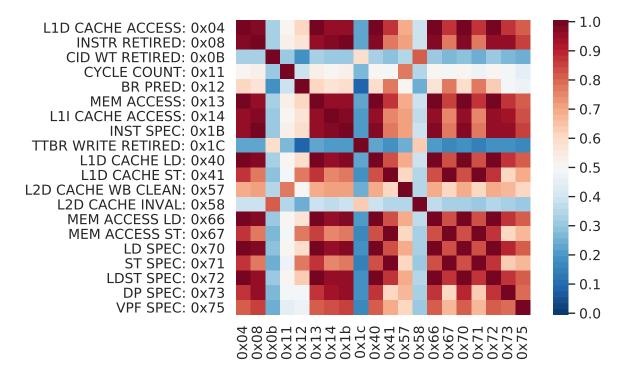

|    | 6.2.2      | PMC Selection                             | 87 |

|    | 6.2.3      | MLP Training                              | 88 |

|    | 6.2.4      | Run-time power and performance estimation | 89 |

|    | 6.3: Exp   | erimental Results                         | 89 |

|    | 6.3.1      | Workload description                      | 90 |

|    | 6.3.2      | Evaluation on the A15 cluster             | 91 |

|    | 6.3.3      | Evaluation on the A7 cluster              | 96 |

|    | 6.4: Con   | clusion                                   | 98 |

| 7: | Conclusio  | $\operatorname{Dn}$                       | 99 |

|    | 7.1: Rem   | arks                                      | 99 |

| REFERENCES | • |  | • | • | <br>• |  | • |  |  | • | • | • | • | • | • | • | • | • | • | • | • |  | _ | 100 |

|------------|---|--|---|---|-------|--|---|--|--|---|---|---|---|---|---|---|---|---|---|---|---|--|---|-----|

| VITA       |   |  |   |   |       |  |   |  |  |   |   |   |   |   |   |   |   |   |   |   |   |  | - | 114 |

### LIST OF TABLES

| TA  | BLE                                                                             | PAG | $\mathbf{E}$ |

|-----|---------------------------------------------------------------------------------|-----|--------------|

| 3.1 | Application classification (L = memory intensive, C = cache intensive and N     | =   |              |

|     | compute intensive)                                                              | •   | 21           |

| 3.2 | Qualitative comparison of application classes based on their contentiousness ar | nd  |              |

|     | sensitivity on the shared resources.                                            | •   | 27           |

| 3.3 | Server characteristics used for the evaluation.                                 | •   | 42           |

| 4.1 | System specifications for evaluated server platform                             | •   | 62           |

| 4.2 | High Priority Applications and Datasets                                         | •   | 65           |

| 4.3 | List of benchmarks in each evaluated mix                                        | •   | 66           |

| 4.4 | Avg High Priority Throughput Gain %                                             | •   | 68           |

| 5.1 | Comparison of different classifiers                                             | •   | 77           |

| 6.1 | Power and $IPS_{total}$ Error Percentage for A15 and A7 Clusters                | •   | 88           |

| 6.2 | Benchmarks & datasets used for the A15 cluster                                  |     | 91           |

| 6.3 | Benchmarks & datasets used for the A7 cluster                                   |     | 91           |

| 6.4 | Joint run-time constraints for different scenarios on A15 cluster               |     | 92           |

### LIST OF FIGURES

| FIG  | URE PA                                                                                                                     | GE |

|------|----------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Processor trends related to Moore's Law [1]                                                                                | 2  |

| 3.1  | Performance of the 35 co-scheduling scenarios compared to the optimal case. $% \left( {{{\rm{cons}}} \right) = 0} \right)$ | 22 |

| 3.2  | Behavior of the four identified classes under different pressure (max memory                                               |    |

|      | read bandwidth = $13.6 \text{ GB/s}$ , LLC = $15.36MB$ ).                                                                  | 26 |

| 3.3  | Memory bandwidth sensitive applications are not affected when the overall                                                  |    |

|      | bandwidth is less than the maximum available (33 GB/s). $\ldots$                                                           | 28 |

| 3.4  | LLC sensitive applications are not affected when the overall pressure is less than                                         |    |

|      | the LLC size (15.36 MB)                                                                                                    | 29 |

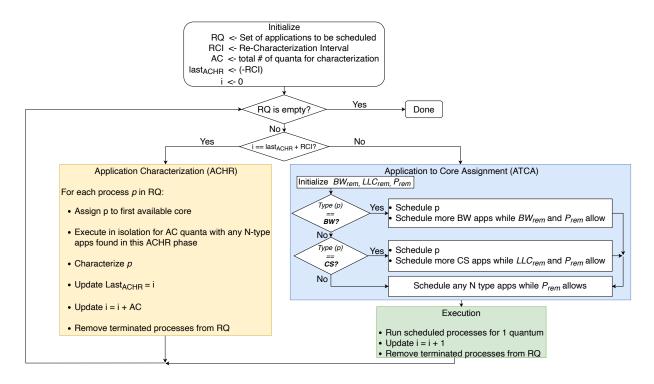

| 3.5  | Flowchart for Dynamic Pressure-Aware Scheduling Policy                                                                     | 36 |

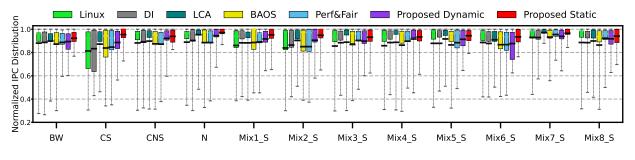

| 3.6  | IPC distribution for single threaded workload mixes for Server 1                                                           | 43 |

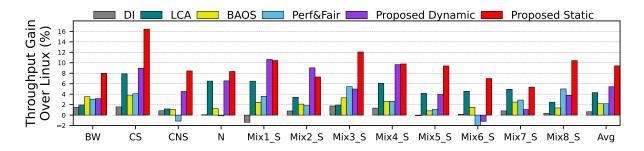

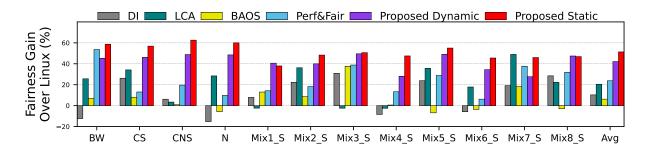

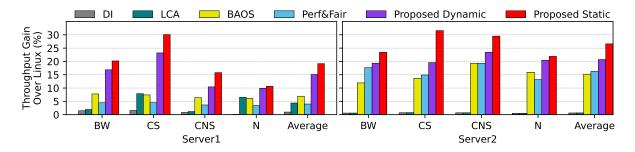

| 3.7  | Throughput gain over Linux for single-threaded workloads for Server 1 $\ . \ . \ .$                                        | 44 |

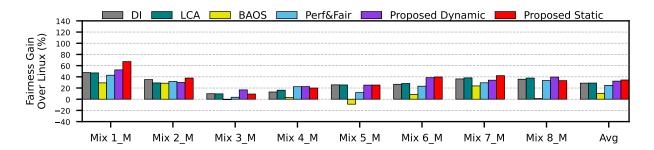

| 3.8  | Fairness gain over Linux for single-threaded workloads for Server 1                                                        | 45 |

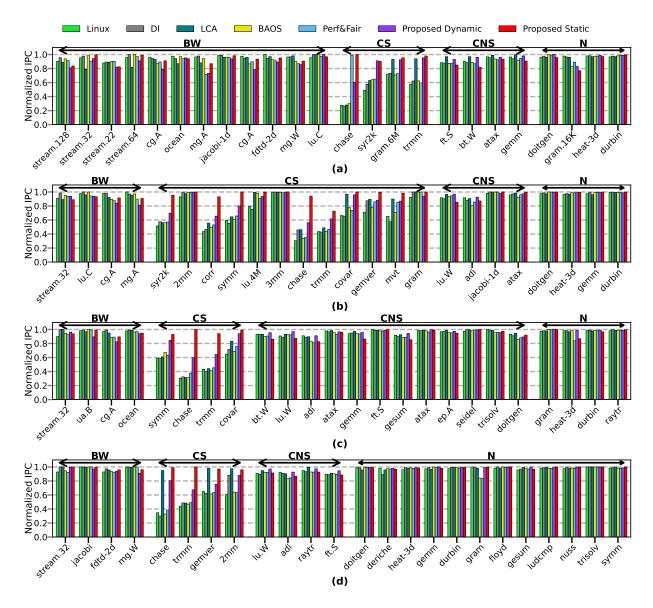

| 3.9  | Detailed performance for BW/CS/CNS/N-dominated mixes: (a) BW-dominated;                                                    |    |

|      | (b) CS-dominated; (c) CNS-dominated; and (d) N-dominated for Server 1                                                      | 47 |

| 3.10 | Throughput gain over Linux for single-threaded workloads on Server 2                                                       | 48 |

| 3.11 | Fairness gain over Linux for single-threaded workloads on Server 2                                                         | 49 |

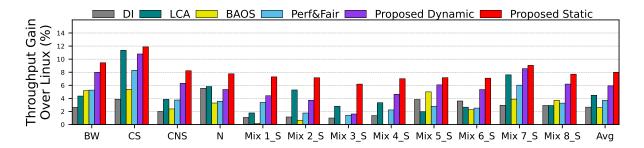

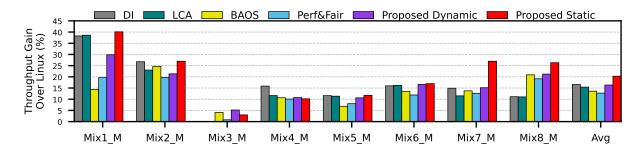

| 3.12 | Throughput gain over Linux for multi-threaded workloads on Server 2. $\ldots$                                              | 49 |

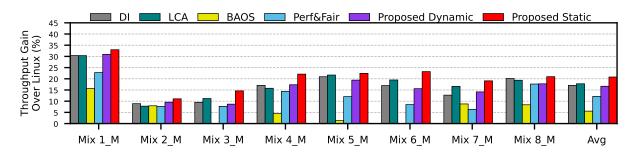

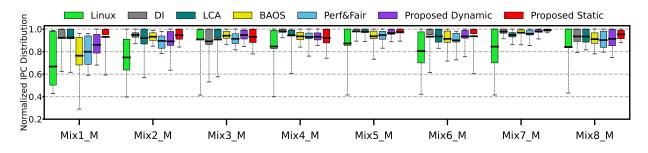

| 3.13 | IPC distribution for multi-threaded workload mixes on Server 1 $\ldots \ldots$                                             | 50 |

| 3.14 | Throughput gain over Linux for multi-threaded workloads on Server $1$                                                      | 51 |

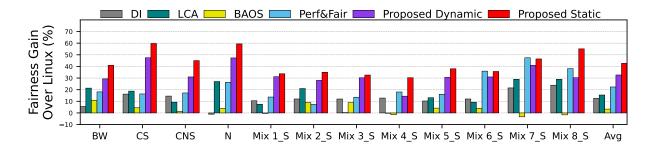

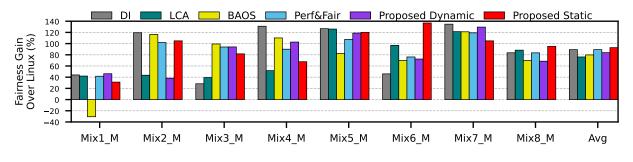

| 3.15 | Fairness gain over Linux for multi-threaded workloads on Server 1                                                          | 51 |

| 3.16 | Fairness gain over Linux for multi-threaded workloads on Server 2                                                          | 52 |

| 3.17 | Enabling hyper-threading results for Server 1 and Server 2                                                                 | 53 |

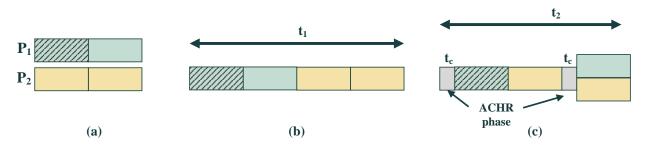

| 3.18 | Example of the effect of dynamic vs. static scheduling: (a) Two BW processes                   |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | P1 and P2 with bandwidth requirement a little less than $L_{BW}/2$ , except for the            |    |

|      | first half of process P1 that has a bandwidth requirement of $L_{BW}$ ; (b) Static             |    |

|      | scheduling; (c) Dynamic scheduling                                                             | 53 |

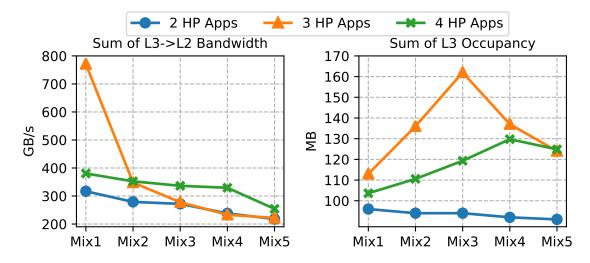

| 4.1  | Sum of individual shared resource requirements for each evaluated application                  |    |

|      | mix                                                                                            | 63 |

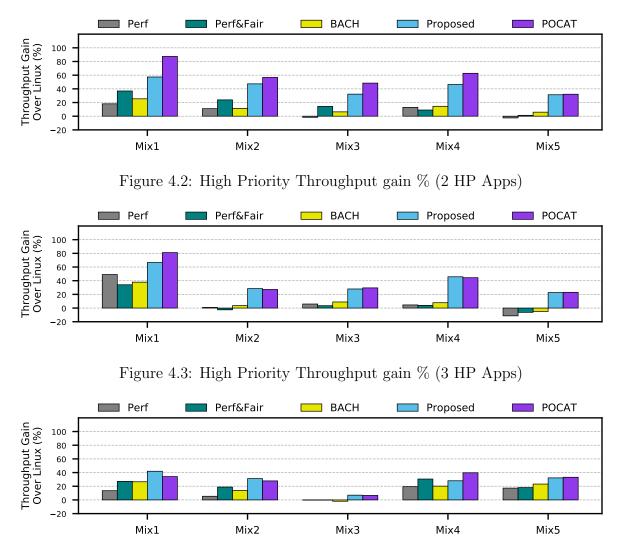

| 4.2  | High Priority Throughput gain % (2 HP Apps) $\ldots \ldots \ldots \ldots \ldots \ldots$        | 67 |

| 4.3  | High Priority Throughput gain % (3 HP Apps) $\ldots \ldots \ldots \ldots \ldots \ldots$        | 67 |

| 4.4  | High Priority Throughput gain % (4 HP Apps) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 67 |

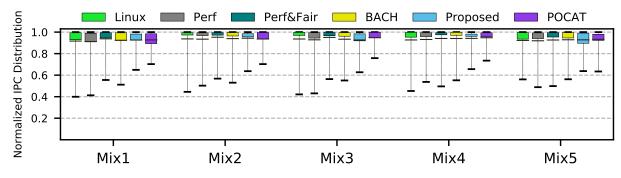

| 4.5  | IPC distribution for all applications in mix (2HP Apps)                                        | 68 |

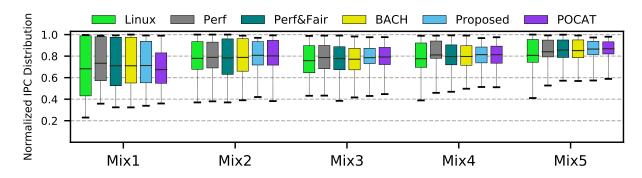

| 4.6  | IPC distribution for all applications in mix (3HP Apps)                                        | 69 |

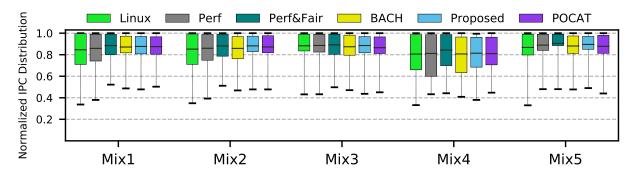

| 4.7  | IPC distribution for all applications in mix (4HP Apps)                                        | 69 |

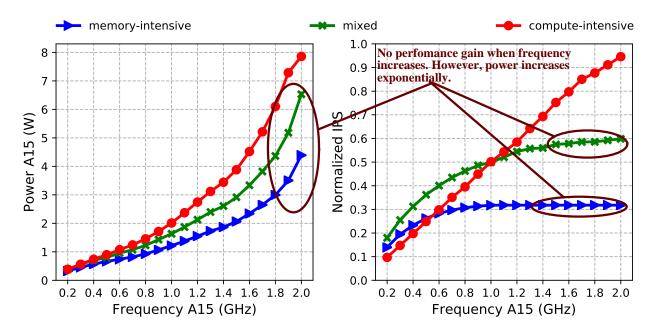

| 5.1  | Power consumption and normalized IPS for different types of application groups.                | 73 |

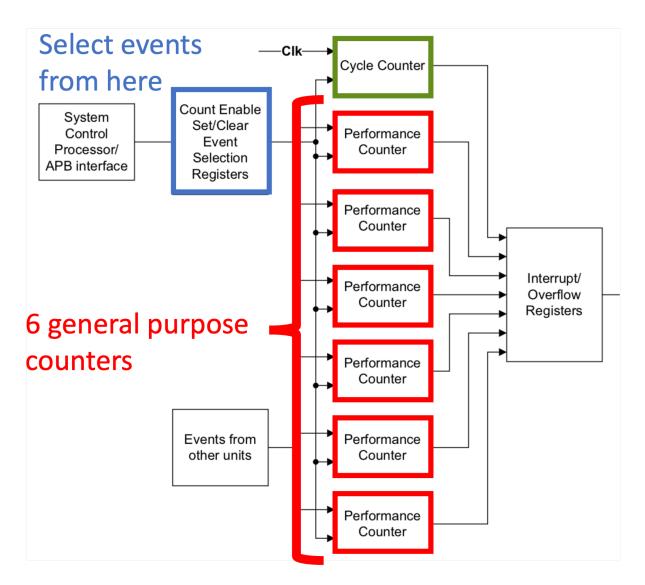

| 5.2  | Block Diagram for Cortex-A15 PMU (ARM PMUv2 architecture)                                      | 75 |

| 5.3  | Top 18 events with minimal variation in recorded counts                                        | 76 |

| 5.4  | MLP classifier training process                                                                | 76 |

| 5.5  | Expected runtime model                                                                         | 78 |

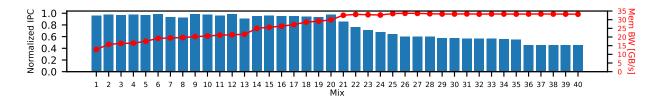

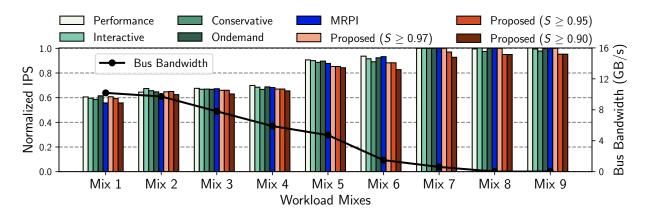

| 5.6  | Normalized IPS and shared bus bandwidth for all application mixes. $\ldots$ .                  | 79 |

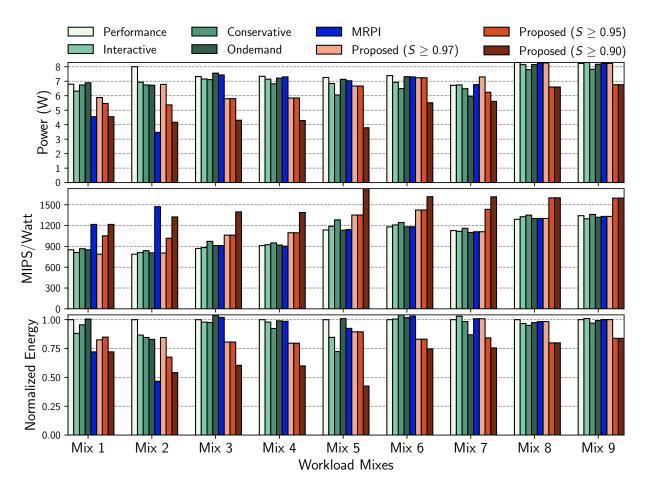

| 5.7  | (a) Power consumption, (b) MIPS/Watt, and (c) Normalized energy                                | 81 |

| 6.1  | Overview of the proposed methodology on the Odroid-XU3 board $\ \ldots \ \ldots$ .             | 85 |

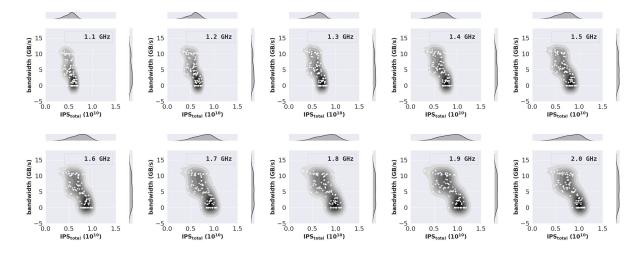

| 6.2  | Distribution of $IPS_{total}$ and memory bandwidth of the created dataset on the               |    |

|      | A15 cluster using kernel density estimation. Each group (denoted by a white                    |    |

|      | cross) utilizes all four cores of the cluster                                                  | 86 |

| 6.3  | Pearson's Product Moment Correlation for a subset of A15's PMCs                                | 87 |

| 6.4  | Example constraints for A15 cluster                                                            | 89 |

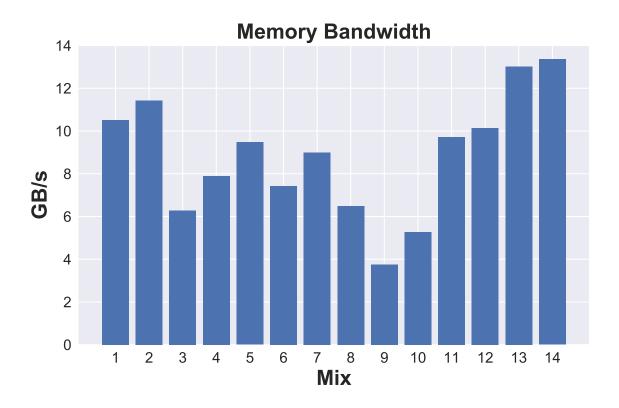

| 6.5  | Memory bandwidth (shared-resource utilization) for applications mixes used for                 |    |

|      | the A15 cluster.                                                                               | 92 |

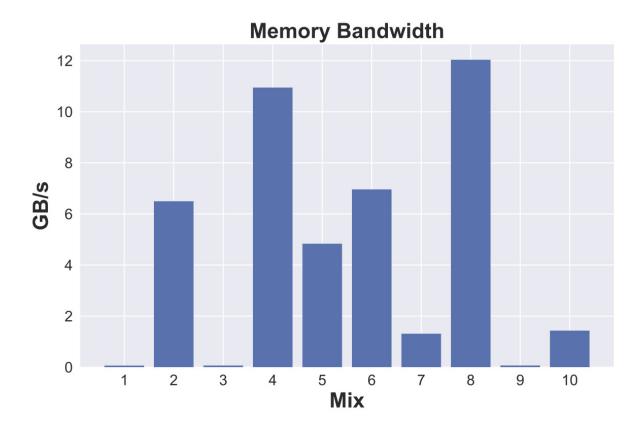

| 6.6 | Memory bandwidth (shared-resource utilization) for applications mixes used for  |    |

|-----|---------------------------------------------------------------------------------|----|

|     | the A7 cluster.                                                                 | 93 |

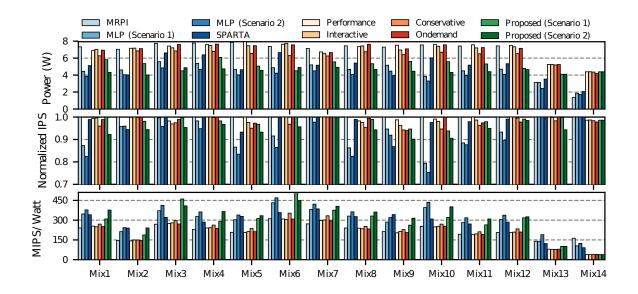

| 6.7 | (a) Power consumption; (b) performance in terms of normalized IPS; and (c)      |    |

|     | power efficiency in terms of $MIPS/WATT$ for 14 random application mixes on     |    |

|     | the A15 cluster under two constraint scenarios (Table 6.4). Each mix consist of |    |

|     | four concurrent executing applications                                          | 94 |

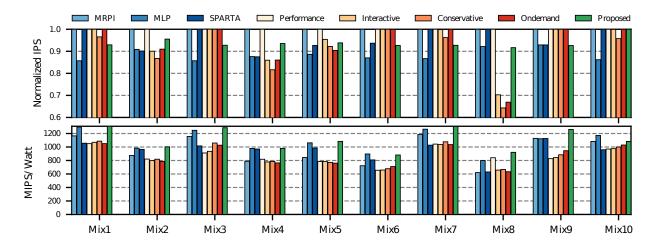

| 6.8 | (a) Performance in terms of normalized IPS and (b) power efficiency in terms    |    |

|     | of $MIPS/WATT$ for 14 random application mixes on the A7 cluster for the        |    |

|     | selected scenario. Each mix consist of four concurrent executing applications . | 94 |

## LIST OF ALGORITHMS

| ALGORITHM PA |                                    |  |    |  |  |  |  |  |  |  |  |  |

|--------------|------------------------------------|--|----|--|--|--|--|--|--|--|--|--|

| 1            | Static Scheduling Policy           |  | 35 |  |  |  |  |  |  |  |  |  |

| 2            | Proposed dynamic scheduling policy |  | 38 |  |  |  |  |  |  |  |  |  |

| 3            | Proposed scheduling policy         |  | 61 |  |  |  |  |  |  |  |  |  |

## CHAPTER 1 INTRODUCTION

This chapter provides technological and historical background into the development of Chip Multi-Processor (CMP) architectures and discusses the importance of exploring both resource- & power-aware scheduling techniques for current and future CMP architectures.

### 1.1 DECLINE OF SINGLE-CORE ARCHITECTURES

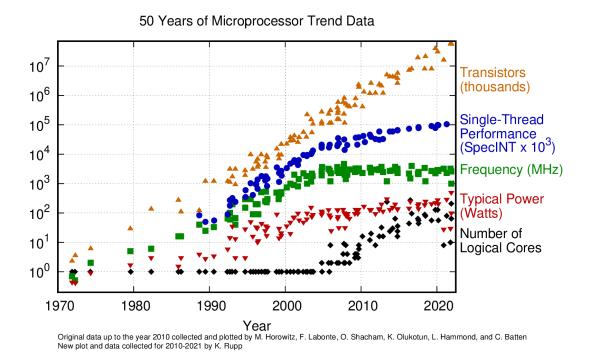

From the late 1990's, chip manufacturers began development of multi-processor architectures to address the growing shortcomings of existing single-core designs. Among the major challenges to improving single-thread performance were the diminishing returns on application performance at higher clock frequencies and the growing difficulty of heat dissipation due to unprecedented device densities on the die [2]. In the preceding decades, chip manufacturers, consumers, and enthusiasts alike had become accustomed to large increases in clock speed with each successive generation of processors. However, at the turn of the century, the industry inevitably experienced a slowdown in the growth of both clock frequency and single-thread performance, despite steady advances still continuing at the device (transistor) level. This led many observers to speculate an imminent end to the performance predictions associated with Moore's Law. Figure 1.1 shows a compilation of nearly 50 years of data depicting raw transistor counts and the corresponding clock frequencies and single-thread performance (measured by SpecINT benchmarks [3] ). The key detail in the graph is the discrepancy between the growth of raw transistor count compared to the other metrics such as single-thread performance and clock frequency.

In addition to heat dissipation challenges, single-thread performance was also increasingly bottlenecked by the growing divide between main memory and CPU speeds (i.e., the Memory Wall). For example, from 1986 to 2000 the average CPU clock speed increased by 55% annually while the speed of memory accesses increased at only 10% [4].

Figure 1.1: Processor trends related to Moore's Law [1]

In order to "squeeze-out" additional performance gains from single-core architectures, chip designers experimented with various techniques to increase parallelism at the instruction level. Among the developments were deep execution pipelines, superscalar architectures, Very Long Instruction Word (VLIW) architectures, and proprietary systems such as Explicitly Parallel Instruction Computing (by Intel) [5]. While these approaches improved single-thread performance, they came at the cost of greater hardware complexity and a corresponding increase in power consumption. One example of this approach was the introduction of a 31-stage pipeline in the final variations of Intel's *Pentium* line of processors [6].

### 1.2 CHIP MULTI PROCESSORS

One approach to improving performance without increasing raw clock frequency (and subsequent power consumption and heat) was to distribute computational workloads among several different processors. Each process could then be executed on its own distinct *core*

and could communicate with concurrently executing processes through message-passing or accessing shared memory locations. Although the concept of multiprocessing itself had been known since 1843 [7], manufacturing an entire multiprocessor system on a single chip was both an unprecedented challenge as well as a significant breakthrough in the history of computing. The first commercially available Chip Multi-Processor (designed for servers and workstations), IBM's *Power4* was released in 2001 [8]. It comprised two 64-bit cores embedded onto the same die, sharing a high-speed L2 cache and buses for inter-core communication at rates of over 35GB/s [8]. Realizing the obvious advantages, other chip manufacturers such as Intel and Motorola also adopted the CMP architectural paradigm.

The multi-processor approach of using a number of simpler and less powerful cores offered considerable practical benefits to the end user. Novel CMP architectures were developed to address the primary obstacles to single-thread performance improvement, namely the fast-approaching Memory and ILP Walls, and reduction of dynamic power consumption to lower the amount of heat generated by the chip (i.e., power wall). CMPs also addressed the discrepancy between processor speed and rate of memory accesses to a large extent. Combining multiple CPUs onto a single die allowed for superior cache coherency, while simply having multiple simpler cores increased the overall rate of memory accesses.

Combined with the changing landscape of consumer computing in the mid-2000's, CMP architectures facilitated several breakthroughs in the field of embedded systems. The era of mobile computing, Internet-of-Things (IoT), and bio-medical electronics were made possible in part by the development of ultra low-power multiprocessor architectures. Despite requiring a more complex manufacturing process, the performance benefits of CMPs were substantial enough to quickly make them a staple of modern consumer electronics. Additionally, CMPs made multitasking the norm rather than a rare exception for embedded systems.

### 1.3 CHIP MULTI PROCESSOR CHALLENGES

Despite their significant advantages, the rise of CMP architectures came at the cost of higher hardware and software complexity. As CMPs enabled multiple processes to be executed in parallel, one of the major software challenges was to determine how concurrently running applications might affect the performance and power consumption of one another. Despite each process being able to run on its own core, certain resources like caches, internal buses, and main memory must still be shared among concurrently executing processes to ensure design simplicity and enable multi-threaded applications to boost performance by sharing a common cache [9]. This means that individual processes may have to 'contend' for control of the limited resources, resulting in a potential drop in overall performance. In some cases, the threads of multi-threaded applications may interfere with each other if fine-grained resource management is not considered. Contention for allocation of shared resources would also lead to novel power/thermal management challenges such as the problem of reducing *dark silicon* areas on the chip. Another problem arising due to shared-resource contention was the increased difficulty of enforcing priority and fairness among concurrent processes due to increased unpredictability (i.e., non-determinism). This would especially affect the functioning of the rapidly growing cloud services industry which relies on specific Service-Level Agreements (SLAs) for offering different tiers of performance.

Although resource allocation was also a requirement in single-core processors, the dynamic and parallel nature of CMP process execution added a significant level of complexity to the process. As modern processors follow a non-deterministic flow of execution, the number and type of processes being executed on a CMP can vary greatly between successive time periods, leading to cases where applications interfere with each other. In contrast, the amount of computing resources available to a process in single-core execution is usually well known, with the details varying only slightly between architectures.

### 1.4 CONCLUSION

Shared resource contention is the primary bottleneck to concurrent application performance in CMPs. Sophisticated management of shared resources can yield diverse benefits such as improved performance, higher throughput, better enforcement of fairness and priority, lower impact of non-determinism on dynamic execution, lower power consumption, lower percentage of dark silicon, and generally higher performance-per-Watt for the overall system. Additionally, fine-grained tracking and allocation of shared resource usage can aid in the development of dynamic frequency-scaling approaches. When used effectively, Dynamic Voltage & Frequency Scaling (DVFS) capability can be used to lower power consumption without incurring any penalty in performance.

Given the diverse benefits, it is imperative to develop sophisticated scheduling algorithms that account for both the efficient allocation of shared resources as well as the judicious use of higher clock frequencies.

#### 1.5 RESEARCH QUESTIONS

- 1. Regarding the relationship between application performance and shared-resource contention on CMPs:

- (a) To what extent, if any, do concurrently executing applications affect the performance of one another? How can the level of interference be quantified?

- (b) What role do shared resources play in facilitating (or hindering) concurrent application execution?

- (c) What is the performance benefit of parallel execution on CMPs compared to time-multiplexed single-core multitasking?

- 2. What is the impact of shared-resource contention on the overall power consumption of CMPs when executing concurrent workloads?

- 3. Regarding improvement in application performance per unit of power consumed:

- (a) Can management of shared-resource contention help guide dynamic scaling of clock frequency (using DVFS)?

- (b) Can power consumption be reduced without affecting concurrent application performance?

- (c) Is it practical to scale the operating frequency at runtime?

- (d) What is the trade-off between overhead vs performance improvement when using power-aware scheduling guided by resource pressure management?

- 4. Using resource-aware scheduling, what is the optimum combination of performance and power consumption that can be obtained?

### 1.6 CONTRIBUTIONS

- A holistic analysis of the impact of shared-resource contention on concurrent application performance in CMPs. Identifying and quantifying a given process's contentiousness and sensitivity to resource pressure. Based on this analysis, development of two fine-grained pressure-aware scheduling methodologies to maximize overall throughput and fairness.

- 2. A methodology for enforcing minimum performance thresholds in an execution framework comprising two priority levels for processes (high and low). Our approach ensures that high-priority applications meet their performance requirements while simultaneously preventing low-priority applications from experiencing resource starvation. This approach also results in a net improvement in overall throughput.

- 3. A run-time algorithm for proactively scaling operating frequency based on Performance Monitoring Counter (PMC) values to improve the overall power efficiency (IPS-per-Watt) of a clustered RISC CMP architecture.

- 4. (a) A mechanism to predict the power consumption and performance of concurrent

workloads at all available operating frequencies of a CMP, using PMC counts as inputs.

(b) A scheduling methodology which selectively switches frequency to satisfy both performance and power constraints

## CHAPTER 2 LITERATURE REVIEW

Several works have sought to address the multifaceted problem of how to best manage shared resources on chip-multiprocessors in order to achieve a broad variety of goals such as improving tail latency, maximizing IPC, enforcing fairness, regulating temperature, and avoiding hot-spots. This chapter analyzes these approaches from two broad perspectives improving purely performance-related metrics such as IPC and fairness, and improving power-related metrics such as the total power consumption of the chip, or the power consumption of a specific component on the chip. There is significant overlap between some works, which may fit into both sections.

### 2.1 CONTENTION-AWARE SCHEDULING

Most works that address shared-resource contention in CMPs use two main strategies resource utilization monitoring and application classification.

In [9,10], the authors aim to improve the fairness of resource allocation among concurrent applications by means of a sampling-based approach. For each time quantum, concurrent applications are profiled and re-scheduled if needed to minimize the amount of resource-based interference between them. The methodology in [11] presents a distributed resource allocation technique for multi-threaded applications using pool-based clustering of the available cores. Clusters are created based on system's characteristics and the allocation of cores is performed in a manner so as to increase resource utilization and reduce fragmentation. The authors of [12] use an IPC-per-core based approach, along with application classification for determining the ideal number of threads as well as the best thread-to-core mapping for a given set of workloads.

Several methodologies classify the memory, cache, and performance usage patterns of applications in order to schedule them into contention-minimizing groups. The authors

of [13] propose a memory-aware scheduling methodology which monitors realtime memory usage and cache miss rates without the need for application profiling. A drawback of this approach is that it only works for cache architectures with LRU policies. Another work which utilizes resource monitoring is [14]. This methodology relies upon the L1 cache bandwidth to identify and minimize shared resource contention. However, the authors do not consider other shared resources such as memory and L2 cache accesses. The authors of [15] proposes a two-tier a methodology to address both shared-resource contention and power consumption of many-core processors. They exploit usage patterns of shared LLC's to schedule the given workloads into groups. The drawback of this approach is that it relies upon per-core voltage monitors, which is not feasible for many CMP architectures [16]. The authors of [17] present a scalable methodology for dynamic resource allocation on CMPs. Although they increase weighted speedup and scheduling fairness, they do not consider power consumption and frequency scaling. The authors of [18] use a machine learning based approach for anticipating the level of shared-resource contention based on past resource allocation statistics. Their use of a runtime global monitoring and scheduling methodology increases the performance overhead considerably. [19] uses a novel MIMO controller methodology to maximize resource allocation efficiency for concurrently executing applications. Although this method improves performance over heuristic approaches, the added hardware required decreases the practicality of this approach. In [20], the authors propose a methodology to improve fairness among concurrently executing applications by using a novel method to quantize execution progress by using instructions-per-second. The applications are then assigned to cores based on progress. The authors demonstrate an 86% improvement in fairness over evaluated schedulers. In [21], the authors develop the progress measurement metric further to create application-to-core mappings that balance both bandwidth and LLC requirements. This method improves average performance gain by 6.3% to 16% while enforcing fairness of execution.

Other works utilize resource monitoring to achieve domain-specific goals such as the

enforcement of priority and maximization of fairness in dynamically scheduled systems. In [22] and [23], the authors aim to reduce the performance degradation of applications due to contention for main-memory bandwidth. The authors of [22] present a scheduling methodology that balances memory bandwidth across all executing applications. In [23], an improvement in performance is achieved by means of a per-core memory regulator and reclaim manager.

Numerous works, such as [24], [25], and [26] aim to improve performance of prioritized applications through hardware-assisted cache partitioning techniques. The authors of [24] present an application categorization methodology based on cache utilization. The applications are scheduled according to their class co-execution characteristics. In both [25] and [26], the authors present a scheduling methodology that uses Intel's Cache Allocation Technology (CAT) to create partitions that reduce contention for the LLC. Furthermore, the authors of [26] demonstrate how their methodology can be used to improve performance for prioritized applications. However, a major drawback of these methods is their need for specialized hardware support. The work presented in [27] proposes three approaches to resource-management for hard real-time embedded systems, with the goal of reducing Worst-Case Execution Time (WCET) and Worst Case Reaction Time (WCRT). It uses the 3-phase task execution model presented in [28], [29], and [30], to perform a contention analysis for the memory bus, a contention analysis for the cache bus, and a formulation for fixed task-priority approach to memory-centric scheduling. The bus contention analysis considers two different memory access models, i.e., dedicated and fair memory access models, built on top of the first-come-first-served (FCFS) bus arbitration policy to achieve its ultimate goal of determining the maximum contention that can be suffered by tasks. The contention analysis for the cache focuses on analyzing cache persistence to determine how LLC misses affect contention on the memory bus, to supplement the earlier analysis of memory bus contention and further improve the estimation of the impact of resource contention on WCRT. The memory-centric scheduling

approach makes use of these analyses to reduce WCRT. [31] presents an approach to enforcing QoS for devices in the cloud-edge continuum. It aims to eliminate or minimize QoS violations due to shared-resource contention on edge devices that execute cloud micro-services. The authors utilize a mapping approach based on reinforcement learning to capture the complex contention behaviors of edge devices that execute co-located and dynamically allocated cloud micro-services. The authors demonstrate a reduction in computational resource usage by 23.9% while maintaining QoS and also improving tail latency. In [32] the authors propose a resource-management system to achieve desired video inference latency and accuracy trade-offs under changing runtime conditions in internet-connected mobile-devices. This work includes a contention-aware scheduling methodology that uses DNN models along with extensive offline profiling and considers resource contention on the CPU, GPU, and memory bus. The authors of [33] present a contention minimization methodology as part of a work to reduce QoS violations while executing processes for cloud micro-services. Their "resource-manager" determines optimal resource allocation based on reinforcement learning, which the authors claim can capture complex contention behaviors. In [34], the authors outline an efficient resource-management mechanism to predict contention-induced performance degradation as part of a larger method to meet specific Service Level Agreements (SLAs) for server utilization when providing Network Function (NF) Virtualization service. Their contention minimization methodology relies on precisely characterizing (1) the pressure each NF applies on the server's shared hardware resources (contentiousness) and (2) how susceptible each NF is to performance drop due to competing contentiousness (sensitivity). They demonstrate a 6% to 14% improvement in server utilization efficiency.

### 2.2 POWER-AWARE SCHEDULING

A number of works address the reduction of power consumption in CMPs while also maintaining a minimum level of performance and/or throughput.

First, regarding the power consumption of clustered multi-processors, the authors of [35] present a methodology that utilizes a PI controller for monitoring and reducing power consumption. However, the individual characteristics of the workloads are not taken into consideration, effectively treating the processor as a 'black box' with two inputs (operating frequency and the predefined control parameters) and one output (power). The authors of [36,37] present a methodology which uses Memory-Reads per Instruction (MRPI) to meet application-specific performance requirements (IPS) and reduce energy consumption by predicting the operating frequency of the processor. Similarly, the authors in [38,39] adjust operating frequency based on the memory accesses and the required response time. However, these approaches allow for significant energy and power reduction only when memory-intensive applications are part of the application mix. Additionally, the authors in [40] present an agent-based power system for frequency selection based on inter-core communication. However, the frequency selection does not consider contention effects. Furthermore, the authors in [18] present a machine learning approach which tracks the usage of multiple shared resources of the processor in order to improve performance of multiprogrammed workloads. However, the authors do not analyze the selection of the inputs to their neural network, making the degree of multicollinearity in the training labels uncertain. Moreover, while the latter tries to improve performance of workloads, it does not consider the trade-off between the increase in performance and power consumption, leading to lowered reduced efficiencies.

The authors of [26] present a contention-aware scheduling policy which leverages Intel's Top Down Microarchitecture Analysis Method (TMAM) for application profiling. The TMAM method allows for obtaining an accurate representation of application's resource utilization which is in turn used to develop their application-to-core placement technique. At run-time, the application groupings are determined by a cost function that seeks to minimize performance (IPC) loss due to contention for the shared LLC. A drawback of this method is that it requires Intel's Cache Allocation Technology (CAT)

support for the processor, available only in specific models. In [41], the authors aim to avoid contention on the LLC by combining detailed resource-utilization information with a resource-aware application-to-core placement policy and use of Intel's Cache Allocation Technology (CAT). Their methodology utilizes a two-step approach which first calculates the ideal cache partition (using hierarchical clustering) and then calculates the ideal application-to-core placement (using a heuristic based on cache-miss curves). The key contributor to overhead is the quadratic-time Look-ahead algorithm used at run-time to determine the best cache partition. When there are more than 8 available applications (and 12-way cache), the scheduling overhead increases significantly, rendering this approach impractical in real-work applications. In addition, this method also requires specialized hardware support (Intel's CAT). Additionally, several other studies have focused on quantifying the impact of cross-core interference and deciding application groupings to to boost application throughput [42, 43, 44, 45, 46]. These works combine varied techniques to reduce the performance impact of shared-resource contention. However, they differ from our proposed approach as they do not holistically monitor contention for all levels of the memory hierarchy. In [47], the authors present a contention-aware scheduler which utilizes cache misses per million instructions as a heuristic for quantifying contention. While this method works successfully for highly memory intensive groups of applications, it yields lower performance for other workload types. In [48], the bandwidth between links of the memory hierarchy is tracked to capture activity of the applications. This method identifies cache-intensive applications and avoids scheduling them with applications that heavily thrash the LLC. However, unlike our proposed static scheduler, this method is less *fine-grained* and cannot detect applications which rely on cache but their cache access pattern makes them less susceptible to LLC interference (cache non-sensitive). In [49] a combination of application profiling and neural networks are used to maximize the performance (Instructions per Second (IPS)) of varied resource-intensive workloads. Although this work demonstrates an increase in performance over Linux scheduler, their

coarse-grained characterization scheme leaves room for further improvements in both individual and overall application performance. A fine-grained application characterization is utilized in [50] to improve the performance (IPC) of prioritized applications executing under shared-resource contention. Even though this method uses fine-grained statistics, its primary goal is to improve performance for specific high-priority applications in a workload, in contrast to our approach which considers workload performance. In [51], the authors present a methodology to improve performance for convolutional neural network workloads on heterogeneous multicore processors. This method explores the operating frequencies of the device, prunes the design space and decides the optimal device configuration according to system objectives (minimize power/maximize performance). Experimental results demonstrate 42.8% to 61.5% reduction in power consumption. The authors of [42] aim to improve the efficiency of shared resource utilization while also preserving the required Quality-of-Service (QoS) (measured by tail latency) of each scheduled application. They accomplish this by extracting the resource-interference profiles of each application using specially developed micro-benchmarks and performing a series of stochastic gradient descent operations to decipher the ideal application-to-core placement. A shortcoming of this approach is that it requires profiling for each application using specially designed benchmarks. This renders the approach impractical in cases where additional CPU time cannot be allocated for separate profiling of applications. The authors of [43, 45] utilize approximate computing techniques to improve resource utilization for shared servers based on CMP architectures. Both works aim to keep performance degradation of each application within specified tolerance limits. They take the performance tolerance threshold (measured in % slack in tail latency) as input and output the ideal application-to-core placement. However, both techniques need to dynamically recompile the applications which increases the run-time overhead and precludes their usage in cases where the source code is restricted. In [46], the authors utilize deep learning techniques in order to anticipate spatial and temporal patterns in application execution that may result in

quality of service degradation in CMP servers. Their method involves obtaining resource utilization information from remote procedure call (RPC) level traces of each scheduled application to proactively detect any upcoming violations in tail latency requirements. In this manner, the authors aim to improve predictability of cloud microservices and prevent any single misbehavior from causing a cascade of QoS violations. The main drawback of this approach is the need for an extremely large dataset for training the Deep Neural Networks (DNNs). Each DNN predictor requires up to 1 week's worth of execution data for training. The authors of [44] propose a method that uses a combination of containers, thread pinning, cache partitioning, frequency scaling, and memory capacity partitioning to allow latency-critical apps and microservices to be co-executed without QoS (tail latency) violations. They begin by performing a comprehensive analysis of resource requirements, contention effects, and sensitivity for different application types. Next, they identify 'fungible' computing resources that can be re-allocated at run-time to provide the necessary resources for applications. The Perf&Fair scheduler [52] uses an online average of performance and fairness as part of a fitness function to schedule applications for each time quantum. However, due to its increased focus on fairness, it generally results in lower overall performance. The BAOS scheduler [22] calculates overall main memory requests and the average main memory bandwidth utilization for each application per quantum. The application with the best fit in terms of bandwidth is selected to run during the following quantum. However, this method cannot prevent memory-intensive applications executing alongside cache-intensive applications, which leads to a drop in performance.

Finally, certain works employ resource-utilization strategies as part of a larger approach to meet domain-specific goals. In [53], the authors present an approach that aims to enforce varying QoS requirements for applications with different levels of execution priority. Their proposed method utilizes a distributed set of *'lightweight performance meters'* on each available core of the system. The performance meters can account for differences in the cores' architecture and help to coordinate overall resource allocation. The

authors were able to demonstrate up to 24% improvement in memory bandwidth utilization while also enforcing QoS (measured in frames per second) for target applications. In [54], the authors express run-time constraints and mine multiple parameters in order to create optimized system- and application-aware operating points. This approach results in a balance between temperature, power consumption, and performance (instructions-per-second), resulting i 15.4% to 35.3% reduction in energy consumption. In [55], the authors propose a technique for improving the energy efficiency of heterogeneous multi core architectures while also maintaining a minimum user-defined fairness of execution. This is achieved through a combination of offline profiling/ application characterization and dynamic frequency scaling. The authors of [56] also present a methodology for improving the power efficiency of heterogeneous multi core processors used for edge-computing purposes. It uses a hardware-tailored multi-task programming model which yields an average of 22% increase in energy efficiency compared to a reference system.

## CHAPTER 3 CONTENTION-AWARE SCHEDULING

Modern CMPs are have been steadily integrating an increasing number of cores into a single socket to address the continually growing demand for higher application performance. Generally, the cores of a CMP share several components of the memory hierarchy such as a Last-Level Cache (LLC) and main memory bandwidth. This allows for considerable gains in multi-threaded application performance, while also helping to maintain overall architectural simplicity. However, a consequence of sharing resources is the inevitable performance bottleneck caused by contention for shared resources among concurrently executing applications. In this chapter, we formulate a fine-grained application characterization methodology that leverages the Performance Monitoring Counters (PMCs) and Cache Monitoring Technology (CMT) available in Intel processors. We utilize this characterization methodology to develop two contention-aware scheduling policies, one static and one dynamic, that co-schedule applications based on their resource-interference profiles. Our approach focuses on minimizing contention on both the main-memory bandwidth and the LLC, by monitoring the pressure each application inflicts on these resources. We achieve performance benefits for diverse workloads, outperforming Linux and three state-of-the-art contention-aware schedulers in terms of system throughput and fairness for both single and multi-threaded workloads. Compared to Linux, our policy achieves up to 16% greater throughput for single-threaded and up to 40% greater throughput for multi-threaded applications. Additionally, the policies increase fairness by up to 65% for single-threaded and up to 130% for multi-threaded ones.

### 3.1 SHARED-RESOURCE CONTENTION

Chip Multi-core Processors (CMPs) have become the dominant architectural choice in the server and desktop processing domains due to their scalable computational capabilities

at steadily decreasing costs. From the late 90's, CMPs began to successfully overcome the performance and heat dissipation bottlenecks faced by single-core designs through the use of sophisticated Thread-Level Parallelism (TLP) and aggressive scaling of cores. Integrating multiple simpler and more energy-efficient cores paved the way for higher performance yields, as greater throughput could be achieved by executing multiple applications in parallel. Performance boosts, energy-efficiency, and cost-effectiveness were some of the advantages that ultimately led to CMPs becoming the dominant design choice in the server and desktop domains.

However, the benefits offered by the CMP architectural paradigm also introduced a new kind of performance bottleneck: *shared-resource contention*. Since the cores of a CMP are not completely independent processors but are instead clustered together to share several components of the memory-hierarchy, contention among applications for access to these resources can result in significant performance degradation. Shared-resource contention can affect the performance of 1. applications executing concurrently on neighboring cores (noisy-neighbor problem), and 2. threads belonging to the same application if the application does not take advantage of fine-grained resource sharing [57].

The first major point of resource contention is the Last Level Cache (LLC) [58,59]. Cache replacement policies attempt to take advantage of temporal and spatial locality by bringing data to the LLC independently from the application level [57]. A thread may evict the data of a neighboring thread and its own data may be evicted by another [58]. The effect of concurrently executing threads competing for space in the LLC has been studied by many different researchers [59,60,61]. Their results demonstrate that the cache miss rate of a thread can vary significantly depending upon its co-runners, resulting in a performance (Instructions Per Cycle (IPC)) penalty which can be as high as 63% in extreme cases [62]. The other major source of resource contention is the main memory bandwidth [22,48,63,64]. Concurrently executing applications on a chip multi-core processor with a shared memory system can suffer performance degradation due to

interference in memory accesses. Authors in [65] demonstrate that the average memory latency of an application can increase up to  $7 \times$  (translated to 60% IPC loss) when running concurrently with another memory-intensive application. Similarly, performance degradation is observed in experiments where bandwidth contention is injected by memory-intensive co-runners (up to 65% IPC drop [22], 2.2× slowdown [63]).

Resource contention can harm the performance of the system in various ways. Some contention-aware approaches target improvements in *resource efficiency and utilization* [66, 67], while others focus on *maximizing throughput* [47, 58, 68] and *balancing fairness* [20, 64, 69]. Previous approaches generally try to address the challenges posed by resource contention in two steps. First, they extract an *interference profile* for each application executed on the CMP platform. These profiles quantify the application's performance when competing with co-runners for allocation of shared resources [70, 71]. For each application, it is important to identify (1) its *sensitivity* to resource contention, and (2) its *contentiousness* [70]. After application characterization, the second step is the development of contention-aware strategies that optimize system performance by determining contention-minimizing application groupings [22, 47, 72].

In this chapter, we present two pressure-aware scheduling policies, one *static* and one *dynamic*, for contention minimization on chip multiprocessor systems. Both policies utilize the inbuilt performance monitoring unit for fine-grained characterization and scheduling of applications based upon the pressure exerted on the processor's shared resources. Specifically, the innovations of our approach are:

• A fine-grained application characterization methodology that leverages hardware Performance Monitoring Counters (PMCs) and Intel's Cache Monitoring Technology (CMT) [73] to differentiate between applications with similar behavior. This approach analyzes the individual pressure exerted on shared resources by each application at run-time, in turn helping to guide the subsequent resource-aware placement of applications.

- Holistic exploration of the performance impact of resource contention among different application classes, instead of only pairs of classes as in previous works. Our approach focuses on monitoring the pressure exerted on *all available shared resources* of the system simultaneously. Particularly, our method accounts for the following factors: (1) resource pressure is generated by applications in different ways, and (2) applications are sensitive to different levels of pressure applied to various parts of the memory hierarchy.

- A *static* contention-aware scheduling policy that co-schedules applications based on their obtained resource-interference profiles. The key idea lies in our observation that applications of certain characteristics can be placed together without loss in performance if their collective resource pressure does not saturate the LLC and/or main memory bandwidth of the CMP platform.

- A *dynamic* contention-aware policy that co-schedules applications at run-time based on their ongoing resource-interference profiles. This policy uses the same characterization and placement principle as the static scheduling policy except that it does not require any previous information about the workload. It boosts the performance of applications that vary their patterns of resource usage frequently. In both scheduling policies, applications time-share the CPU in a way that evenly balances the pressure on the CMP's shared resources.

- Experimental evaluation of various single and multi-threaded application mixes on two different Intel servers with Cache Monitoring Technology (CMT), and comparison of results with the Linux scheduler (CFS [57]) and four state-of-the-art contention-aware schedulers [22, 47, 48, 52].

| Bench.                | MPMI            | LCA [72]       | Sensitivity                   |

|-----------------------|-----------------|----------------|-------------------------------|

|                       | used by DI [47] | classification | classification [70]           |

| stream                | 7,614.064       | L              | Contentious/Non-sensitive     |

| ocean                 | $2,\!936.885$   | L              | Contentious/Non-sensitive     |

| chase                 | 9.040           | С              | Non-contentious/sensitive     |

| gemm                  | 0.272           | С              | Non-contentious/Non-sensitive |

| $\operatorname{trmm}$ | 0.211           | С              | Non-contentious/sensitive     |

| atax                  | 0.167           | С              | Non-contentious/Non-sensitive |

| $3\mathrm{mm}$        | 0.143           | Ν              | Non-contentious/Non-sensitive |

| $2\mathrm{mm}$        | 0.137           | Ν              | Non-contentious/Non-sensitive |

Table 3.1: Application classification (L = memory intensive, C = cache intensive and N = compute intensive).

## 3.2 MOTIVATION: THE EFFECT OF FINER-GRAIN SCHEDULING.

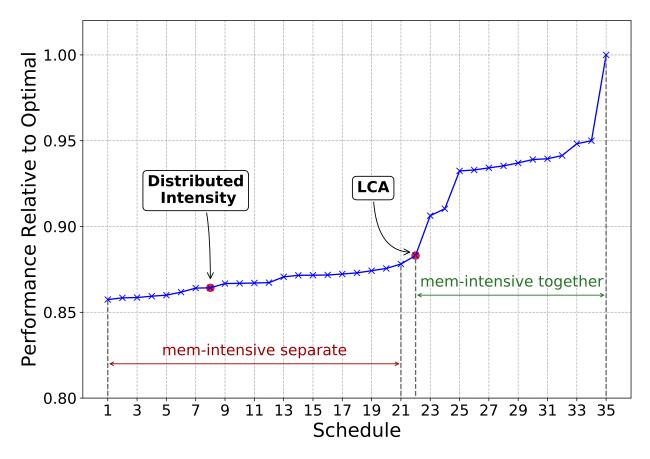

This section contains a motivational example that shows the necessity of fine-grain classification. Table 3.1 depicts a workload of eight applications to be scheduled on a 4-core Intel Core i7 processor with shared LLC and memory controller. The second column indicates the Misses Per Million Instructions (MPMI), which are used as a metric for the Distributed Intensity (DI) contention-aware scheduler [47]. The third column shows the application classification based on the Link and Cache-Aware (LCA) scheduler [72]. The last column depicts the application classification based on contentiousness and sensitivity as presented in [70]. We executed all the 35 possible unique co-scheduling combinations, each one of them consisting of two groups of four applications.

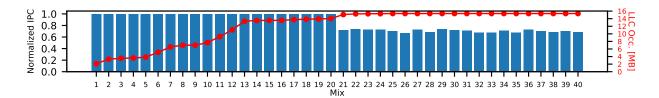

Figure 3.1 depicts the performance of each combination normalized to the optimal. We have also annotated the DI [47] and LCA [72] schedulers based on their decisions. With the DI being in the  $22^{th}$  percentile, we observe that splitting the applications with "high miss rate" to avoid accumulation of memory intensive applications results in a sub-optimal decision. This happens because there are applications with "low miss rate" that show significant reliance on the LLC (C). Consequently, splitting memory intensive applications (2 in our case) and co-execute them with the cache-reliant applications leads to significant interference for the later. Overall, using LLC miss rate as a metric fails to distinguish applications with high LLC utilization from applications that restrict their activity in the lower parts of cache hierarchy.

Figure 3.1: Performance of the 35 co-scheduling scenarios compared to the optimal case.

This problem is addressed by the LCA scheduler, which identifies the cache-intensive applications (C) and avoids co-execution with applications that heavily thrash the LLC (L). However, packing all the C applications together also results in performance losses. This happens because the C applications inflict a lot of pressure on the LLC significantly affecting their performance. Although, this policy is better than DI, as it is located on the  $62^{th}$  percentile, there is still enough room for improvement. We see that solutions that group together the memory intensive applications comprise the top 38% of all the combinations. This is reasonable because the high miss rate applications, which are also classified as contentiousness, are not spread among groups to harm the sensitive

cache-intensive ones. Also, packing them together does not hurt their performance, as the aggregate pressure they put on memory bandwidth can be tolerated and their memory requests can be satisfied.

Considering all the aforementioned observations, we conclude that none of the above classification methodologies alone provide sufficient information for finding the optimal scheduling policy. Thus, it is necessary to find a more fine-grain application classification scheme and examine the performance degradation of an application taking into consideration the following parameters: (1) the pressure the specific application imposes on the shared resources, (2) the total pressure inflicted on the shared resources by the co-runners, and (3) the sensitivity of the application.

# 3.3 PROPOSED METHODOLOGY

In this section, we propose two pressure-aware scheduling approaches, a static and a dynamic one. Both schedulers utilize Performance Monitoring Counters (PMCs) and Cache Monitoring Technology (CMT) to capture the pressure that applications exert on the shared resources and categorize the accordingly. The primary difference between them is that the static scheduler requires an offline profiling stage to determine the interference profile for each application and since it works offline, it can afford to perform complex computations to find the optimum grouping by using Mixed Integer Linear Programming (MILP) (Section 3.3.2). In contrast, the dynamic scheduler does not require any prior information about the workload but determines it at run time. Thus, it can only afford to run a first fit heuristic for scheduling the applications. This generally makes the performance of the static scheduler better than that of the dynamic one. However, the dynamic scheduler yields better performance when executing applications that exhibit frequent phase changes (i.e., changes in resource utilization patterns). Therefore, we split our scheduling methodology into two separate versions for use in the appropriate situation. At their core, both methods use the same underlying principle of fine-grained

23

pressure-aware application placement.

Moreover, both proposed scheduling policies are platform independent. The only prerequisite is the ability to record per-core shared-memory bus bandwidth and last-level cache behavior, which currently is supported by most of systems. Particularly, for Intel x86 processors, this feature is available either through Intel Resource Director Technology (server class architectures) or Intel Performance Counter Monitor Technology (desktop class architectures).

The first part of this section (Section 3.3.1) presents a fine-grained application characterization methodology and analyzes the performance response of co-executing applications to varying levels of shared-resource contention. The second part (Section 3.3.2) presents the proposed pressure-aware static scheduler that focuses on minimizing contention for shared resources. Finally, the third part (Section 3.3.3) presents a modification of the static pressure-aware scheduler that allows for dynamic workload execution (i.e., no prior information about the workload is required at run-time). We utilize the processor's inbuilt Performance Monitoring Unit (PMU) to gather statistics for application characterization, interference analysis, and run-time decision making.

# 3.3.1 Application Characterization & Interference Analysis

Applications competing for the same shared resources can be executed concurrently under certain conditions, leading to an increase in system performance. In order to find which applications are good candidates for each application in a workload, we need to identify 1. the shared resource it utilizes, 2. the amount of pressure it puts on this resource, and 3. its sensitivity when competing with other co-runners for this resource.

### **Applying Pressure**

The first step in our approach is to generate pressure with tunable intensity on the available shared resources of the system in order to test the behavior of applications with

24

widely varying execution characteristics. We record the performance achieved throughout execution of each application while applying varying levels of pressure to the memory hierarchy. As a result, we can identify the source of interference and the amount of pressure at which the applications become vulnerable to a drop in performance. We developed a micro-benchmark resembling the streaming access pattern of the STREAM [74] benchmark. It helps us in profiling the sensitivity of applications under the *whole spectrum of interference* while also being able to gradually increase the intensity of pressure applied on the different shared resources. Furthermore, it has aggressive behavior, meaning that the intensity of resource pressure is maintained when competing with other applications. These characteristics help to accurately identify the level of pressure at which applications become susceptible to performance degradation. We note that application characterization can be affected by the number of threads a given application utilizes, and also by the specific input to the application. Our methodology considers this by treating benchmarks with different numbers of threads and input sizes as separate applications for the purpose of their subsequent scheduling (Sections 3.3.2 and 3.3.3).

#### **Application Characterization**

We consider four classes of applications with regard to their contentiousness and sensitivity to hardware resources (Memory Bandwidth (BW) and Last Level Cache (LLC)): <u>Memory Bandwidth Sensitive (BW)</u>: Applications with a memory usage pattern that resembles a streaming behavior and with a working set larger than LLC size. Consequently, they thrash the LLC (*LLC occupancy* = *LLC size*). <u>LLC Sensitive (CS)</u>: Applications with low memory bandwidth and a working set size that fits entirely within the LLC. They experience severe performance degradation when their cache capacity requirements are not met. <u>LLC Non-Sensitive (CNS)</u>: Applications that have low memory bandwidth and benefit from occupying a certain portion of the LLC, but their performance degradation is not as destructive as for their more sensitive twins (CS). Their cache access pattern makes

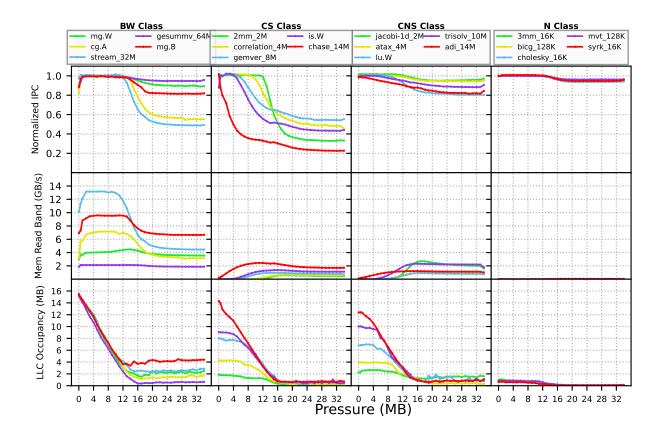

Figure 3.2: Behavior of the four identified classes under different pressure (max memory read bandwidth = 13.6 GB/s, LLC = 15.36MB).

them less susceptible to LLC interference and helps them retain a good performance level, even in the case of excessive LLC thrashing. <u>Neutral (N)</u>: These are applications with negligible memory bandwidth requirements and no dependence on the LLC. Their activity is restricted to the lower parts of the memory hierarchy (L2 and L1 caches).

Table 3.2 depicts a summary in terms of their contentiousness and sensitivity on the shared resources. As experimental validation of these 4 classes, we executed our custom micro-benchmark along with a variety of applications selected from different benchmark suites

(NAS [75], Polybench [76], SPLASH2 [77], Stream [74], and Chase [78]) on a 6-core Intel Xeon E5-2620 v3 server, with LLC size of 15, 360 KB and maximum sustainable memory bandwidth of 33GB/s. More details of our set up can be found in Table 3.3,

| Classes | Memory Bandwidth |              | LLC          |              |

|---------|------------------|--------------|--------------|--------------|

| Classes | Contributes      | Affected     | Contributes  | Affected     |

| BW      | $\checkmark$     | $\checkmark$ | $\checkmark$ | X            |

| CS      | ×                | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| CNS     | ×                | ×            | $\checkmark$ | X            |

| N       | ×                | X            | ×            | ×            |

Table 3.2: Qualitative comparison of application classes based on their contentiousness and sensitivity on the shared resources.

Section 3.4.1. Figure 3.2 depicts the interference profiles of several applications when co-executed with our micro benchmark exerting different levels of resource pressure. We note that the plots shown in Figure 3.2 were individually obtained per application, but were just plotted together in the same figure. In particular, each one of the selected applications is pinned on a core and it is tested against all different contention conditions, from negligible to severe interference in the LLC and memory link. The horizontal axis shows the size of the working dataset (in MB) of the micro benchmark, which is proportional to the level of pressure exerted on shared resources. Working datasets of 16MB and smaller apply pressure to the L1, L2, and L3 (LLC) caches, while working datasets greater than 16MB apply pressure to the memory bandwidth. Specifically, we are interested in the performance (normalized IPC), the memory read bandwidth, and LLC occupancy.

We group the results into four categories, based on the performance response of the tested applications: The first column of Figure 3.2 depicts BW applications with working set larger than the LLC size, that thrash the LLC and have no reliance on it (more in-depth analysis is presented in Section 3.3.1). While their LLC occupancy keeps reducing in proportion to the applied pressure of the micro-benchmark, their IPC is not affected. On the contrary, we observe that their performance is dictated by their achieved memory bandwidth. Reduction in memory bandwidth is directly connected with a drop in IPC, which occurs due to interference in memory requests that cannot be simultaneously satisfied for both the application being tested as well as for the micro-benchmark.

The second column of Figure 3.2 depicts CS applications with low memory bandwidth

Figure 3.3: Memory bandwidth sensitive applications are not affected when the overall bandwidth is less than the maximum available (33 GB/s).

and a working set size that fits entirely within the LLC. We observe that when their cache capacity requirements are not satisfied, due to applied pressure on the LLC, their IPC drops up to 65%. Reduced cache occupancy results in higher number of evicted cache lines, increase in cache misses, and a subsequent increase in memory bandwidth pressure. Note that applications get negatively affected only beyond the point where both their working set size and the pressure applied by the micro-benchmark cannot be collectively accommodated by the LLC. For example, applications with high LLC occupancy (e.g., chase\_14M, is.W) suffer from performance loss at a much lower level of resource pressure than applications with low LLC occupancy (e.g., correlation\_4M, 2mm\_2m).

The third column of Figure 3.2 depicts CNS applications. We observe that their cache access pattern makes them less susceptible to LLC interference and helps them retain a good performance level (IPC drops around 20% in the worst case) even in cases of excessive LLC thrashing (i.e., when micro-benchmark working set  $\geq 16 MB$ , causing high memory bandwidth).

For this reason they are able to retain a good level of performance (IPC drops around 20% in the worst case) even in the case of excessive LLC thrashing (i.e., micro-benchmark working set  $\geq 16 \ MB$ , high memory bandwidth).

The last column of Figure 3.2 depicts N applications. It can be seen that their performance is not affected by the different levels of pressure exerted by our micro-benchmark on shared resources (max IPC drop  $\simeq 5\%$ ) as their working set fits in the lower parts of the memory hierarchy (L2 and L1 caches).

Figure 3.4: LLC sensitive applications are not affected when the overall pressure is less than the LLC size (15.36 MB).

### **Interference Analysis**

In Section 3.3.1, we identified the characteristics and performance response for each class of applications when subject to different amounts of shared-resource pressure. However, not all applications that belong to the same class can be treated uniformly in terms of sensitivity to shared-resource contention, primarily because their slowdown occurs under different levels of pressure. For example, consider the first column of Figure 3.2 which depicts the performance of the BW class of applications to different levels of shared-resource pressure. The application stream\_32M requires the highest memory bandwidth ( $\sim 13$ GB/s) to achieve its ideal performance (i.e., normalized IPC=1) and hence starts to experience performance degradation earlier than all other applications in its class (at pressure  $\sim 12$ MB). Meanwhile, the application cq.A, which requires a much lower memory bandwidth for ideal performance ( $\sim$ 7GB/s), only starts to experience performance degradation beyond resource pressures of  $\sim 14$ MB. Interestingly, the performance of BW applications is not affected as long as the aggregate pressure on the memory controller does not cause complete saturation of the available bandwidth. Therefore, BW class applications can be scheduled simultaneously with negligible performance loss if the individual memory bandwidths are not restricted. We observe the same trend for the CS applications. As long as the aggregate pressure does not exceed the size of the LLC, the application performance is not affected. For example, the application 2mm, which requires an LLC occupancy of 2MB for ideal performance, experiences no IPC drop when the pressure on the LLC is under 12 MB. On the other hand, when the aggregate pressure exceeds the size of the LLC, the performance of the application is significantly affected. For example, genver, which

requires an allocation of 8MB in the LLC, starts to experience performance loss when the applied pressure exceeds 7MB. In general, applications that belong to the same class and have similar activity are not negatively affected if the overall pressure can be tolerated by the shared component. On any other case, the IPC loss is imminent for the co-scheduled applications. Hence, it is very important to introduce an additional feature for each class, which characterizes how much pressure each of the applications inside that class puts on the specific shared resource.