### Southern Illinois University Carbondale OpenSIUC

### Articles

Department of Electrical and Computer Engineering

8-2018

# Digital LDO modelling techniques for performance estimation at early design stage

Haibo Wang zhwang@siu.edu

Stefan Leitner

Follow this and additional works at: https://opensiuc.lib.siu.edu/ece\_articles This paper is a postprint of a paper submitted to and accepted for publication in IET Circuits, Devices & Systems and is subject to Institution of Engineering and Technology Copyright. The copy of record is available at the IET Digital Library.

### **Recommended** Citation

Wang, Haibo and Leitner, Stefan. "Digital LDO modelling techniques for performance estimation at early design stage." *IET Circuits, Devices & Systems* 12, No. 5 (Aug 2018): 655 - 661. doi:10.1049/iet-cds.2017.0429.

This Article is brought to you for free and open access by the Department of Electrical and Computer Engineering at OpenSIUC. It has been accepted for inclusion in Articles by an authorized administrator of OpenSIUC. For more information, please contact opensiuc@lib.siu.edu.

Research Article

## Digital LDO modelling techniques for performance estimation at early design stage

### Stefan Leitner<sup>1</sup>, Haibo Wang<sup>1</sup>

**Abstract:** This work studies the transient responses and steady-state ripples of digital low dropout (LDO) voltage regulators. Simulation models as well as closed-form expressions are provided for estimating the LDO output settling behaviour after load current or reference voltage changes. Estimation equations for the magnitude and frequency of LDO output steady-state ripples are also presented. The accuracy of the developed models is verified by comparing estimation data with results obtained from circuit simulations. The use of the developed estimation equations in design space exploration is also demonstrated.

### 1 Introduction

With the wide use of fine-grain power management in modern VLSI circuits [1, 2], digital low dropout (LDO) voltage regulators are gaining significant research interests and a large number of digital LDO circuits are recently reported [3–17]. The transition from analog to digital LDOs is mainly due to the difficulties in designing power-efficient high-gain amplifiers at low-voltage and advanced technology nodes. Such high-gain amplifiers are crucial in analogue LDOs for minimising the difference between the LDO output voltage and input reference  $V_{\rm ref}$ . Such difference is called error voltage and denoted as  $V_{\rm err}$  [18].

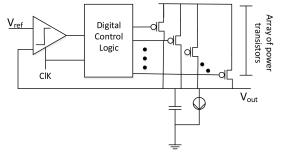

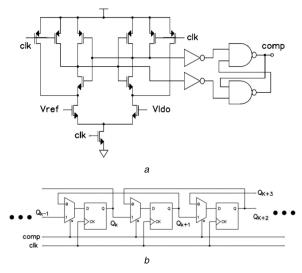

In digital LDO circuits, comparators [3] or voltage controlled oscillators [4] are often used to detect or measure  $V_{\rm err}$ . Also, instead of a single large power device, a digital LDO uses an array of small power transistors, which can be individually controlled by digital signals. Fig. 1 shows a simplified digital LDO circuit to illustrate its operation [3]. If the LDO output is higher than  $V_{\rm ref}$ , the comparator output will cause the digital control logic to decrease the number of conducting power devices; otherwise, the control circuit turns on more power devices. By this feedback mechanism, the digital LDO output is kept at the level of  $V_{\rm ref}$ .

Unlike the high-gain amplifier in an analogue LDO circuit, whose output is proportional to  $V_{err}$ , the comparator in a digital LDO circuit only detects if  $V_{err} > 0$  or  $V_{err} < 0$ . As a result, the feedback factor of the digital LDO control loop is not constant, making it more challenging to derive the closed-loop transfer function of the digital LDO control loop. Meanwhile, estimating digital LDO transient behaviour from its open-loop transfer function is not accurate because previously established methods for predicting transient behaviour from open loop transfer functions are all based on the assumption that the feedback factor does not change during the system settling process [19]. Our early work developed a piecewise analytical model for predicting digital LDO

Fig. 1 Simplified digital LDO circuit

Received on 13th October 2017 Revised 13th February 2018

Accepted on 7th March 2018 doi: 10.1049/iet-cds.2017.0429

ISSN 1751-858X

www.ietdl.org

output settling behaviour after a load change [20]. With approximating the on-resistance of the power devices as constant R, closed-form expressions for estimating the maximum ripple voltage and settling time are derived [20]. In this work, the previous piecewise analytical model is improved by considering the dynamic changes of the equivalent on-resistance of the power device array. Also, the model is extended to predict the LDO transient behaviour after voltage reference changes. Furthermore, this work studies the steady-state output ripples and presents estimation equations for ripple magnitude and frequency. The accuracy of the developed models and equations is validated by comparing with circuit simulations. The use of the developed model for early design space exploration is also demonstrated.

This paper is organised as follows: Section 2 reviews related work on modelling digital LDO circuits. The model developed in our early work is also briefly discussed in this section. The improved model that considers the changes of equivalent onresistance of the power device array is discussed in Section 3. Techniques to model LDO transient behaviour in responding to reference voltage changes are presented in Section 4. Methods for estimating digital LDO steady-state ripples are described in Section 5. The validation of the developed models and the application of the models in design space exploration are presented in Section 6. The paper is concluded in Section 7.

### 2 Related work

A number of works that develop analytical models for LDO circuits have been reported in literature. In [21, 22], comprehensive frameworks for analysing the stability of LDOs with active feedback compensation techniques are presented. Also, techniques for modelling LDO susceptibility to electromagnetic interference are discussed in [23]. Complimentary to these techniques, this work develops models for estimating digital LDO transient behaviours, such as ripple magnitudes after load current or voltage reference changes. Recently, various techniques to enhance LDO transient response, such as using dual control loops in [22], dynamic biasing in [24], or event-driving logic in [25], have been reported. Such enhance techniques can be included LDO modelling as shown in [22, 25].

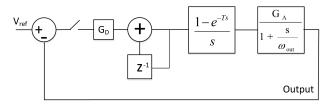

To capture the discrete-time behaviour of circuit blocks used in digital LDOs, z-domain models are often used in digital LDO models. For the circuit shown in Fig. 1, the comparator and the control logic can be modelled by z-domain expressions. Meanwhile, the circuit at the LDO output node is a continuous-time circuit that can be described by an s-domain function. Fig. 2 shows the system-level model of the digital LDO, assuming that the digital control logic is implemented by bi-directional shift

Fig. 2 Digital LDO system-level model [6]

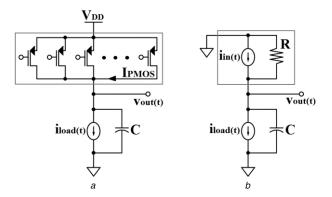

**Fig. 3** *Circuit model for LDO output node* (*a*) LDO output node circuit, (*b*) Simplified circuit model

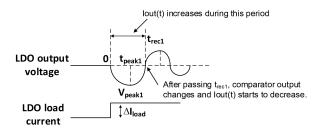

Fig. 4 LDO output response to a load current increase

registers [3]. In the model, the comparator is represented by a subtraction operation. The output of the control logic is effectively the accumulation of the comparator output over time and hence is modelled by a digital integrator followed by a zero-order hold function.  $G_D$  represents the gain of the control logic, which is larger than one when LDO transient response enhancement techniques are used.

The LDO output node is modelled by a first-order linear system with transfer function  $(G_A/1 + (s/\omega_{out}))$ , where  $\omega_{out} = (1/R \cdot C)$ , Rand C are the LDO output resistance and load capacitance, respectively.  $G_A$  is the proportional constant that relates the numerical value of the digital control output and the LDO output voltage. By translating the above s-domain expressions into zdomain functions, the z-domain open-loop transfer function of the digital LDO can be derived as [6]

$$\mathrm{TF}(z) = \frac{G_{\mathrm{D}} \cdot G_A}{(z-1)\left(z-\mathrm{e}^{-(\omega_{\mathrm{out}}/f_{\mathrm{clk}})}\right)} \tag{1}$$

where  $f_{\rm clk}$  is the clock frequency of the circuit. The open-loop transfer function has two poles: one is located at the unit cycle and the other is at  $e^{-(\omega_{\rm out}/f_{\rm clk})}$ . The expression of the second pole reveals some insights about the digital LDO settling behaviour as discussed in [6]. Alternatively, if we substitute  $z^{-1}$  by  $e^{-s/f_{\rm clk}}$ , the above transfer function can be translated into an s-domain expression and it is used to study the LDO stability in [5]. Nevertheless, the difficulty to use such open-loop transfer

functions to predict digital LDO transient responses after load or reference changes is that the feedback factor is not constant during the settling process as discussed earlier.

The piecewise analytical model developed in [20] focuses on the voltage and current relation in time domain. It models the LDO output node using the circuit in Fig. 3b. Following the small signal analysis principle, it treats steady values as 0 and focuses on the changes of signals. Hence

$$i_{\rm in}(t) - \frac{v_{\rm out}(t)}{R} = i_{\rm load}(t) + C \cdot \frac{\mathrm{d}(v_{\rm out}(t))}{\mathrm{d}t} \tag{2}$$

$$\frac{\mathrm{d}(i_{\mathrm{in}}(t))}{\mathrm{d}t} = \kappa \cdot I_{\mathrm{PMOS}} \cdot f_{\mathrm{clk}} \tag{3}$$

where  $i_{in}$  and  $i_{load}$  are the currents conducted by the power devices and the load current, respectively; *R* is the equivalent on-resistance of the combined conducting power devices;  $I_{PMOS}$  is the current conducted by a single power transistor; and  $\kappa$  is 1 or -1 depending on whether the number of conducting power transistors is increasing or decreasing. Both this approach and the modelling techniques in [25] start from the current and voltage relation in time domain. However, they focus on different perspectives of LDO operation and use different analysis methods. The discussion in [25] focuses on LDO stability and relies on a state space model. Our model in [20] focuses on LDO settling parameters and involves deriving piecewise expressions to approximate LDO output waveforms.

Fig. 4 illustrates the LDO output response to a step increase on the load current. Immediately after the load current increase, the LDO output  $V_{out}(t)$  becomes lower than  $V_{ref}$  and the LDO starts to turn on more power devices, hence  $\kappa = 1$ . When  $V_{out}(t)$  reaches its valley denoted by  $V_{peak1}$  in Fig. 4,  $i_{in}(t)$  is increased to the level of  $i_{load}(t)$ . However, the LDO will continue to increase  $i_{in}(t)$  before  $V_{out}(t)$  crossing the  $V_{ref}$  level; and the extra current helps bring  $V_{out}(t)$  back to the desired  $V_{ref}$  level. After  $V_{out}(t)$  exceeds the  $V_{ref}$ level at time  $t_{rec1}$ ,  $V_{out}(t)$  will continue to increase because  $i_{in}(t) > i_{load}(t)$ . Meanwhile, the LDO starts to decrease the number of conducting power devices and  $\kappa = -1$ . This mechanism leads to the voltage ripples at the LDO output when it responds to a load current change.

Owing to the changes of  $\kappa$  value, the  $V_{out}(t)$  expression has to be derived in a piecewise manner. For the example illustrated in Fig. 4, the  $V_{out}(t)$  expression during the time period from 0 to  $t_{rec1}$  can be derived as [20] (see (4)) where

$$X = -\Delta i_{\text{load}} \cdot R - I_{\text{PMOS}} \cdot f_{\text{clk}} \cdot R^2 \cdot C$$

$$Y = I_{\text{PMOS}} \cdot f_{\text{clk}} \cdot R$$

$$Z = \Delta i_{\text{load}} \cdot R^2 \cdot C + I_{\text{PMOS}} \cdot f_{\text{clk}} \cdot R^3 \cdot C^2$$

(5)

With the help of the above equations, the peak voltage value  $V_{\text{peak1}}$  and the time that it reaches the peak,  $t_{\text{peak1}}$ , during this selected time period can be solved by  $(dv_{\text{out}}(t)/dt) = 0$ . Similarly, the voltage peaks and their corresponding times within other time periods can be derived. The work in [20] also shows that the peaks of the voltage ripples in LDO settling process decay exponentially with time and an expression for estimating LDO settling time after load change is also derived.

### 3 Modelling LDO transient response to load current change

The previous piecewise analytical model [20] assumes that R has a constant value during the LDO output transition period. Since R is

$$v_{\text{out}}(t) = X + Y \cdot t + \frac{Z}{R \cdot C} e^{-(t/R \cdot C)}$$

$$= I_{\text{PMOS}} \cdot f_{\text{clk}} \cdot R \cdot t - (\Delta i_{\text{load}} \cdot R + I_{\text{PMOS}} \cdot f_{\text{clk}} \cdot R^2 \cdot C) \cdot (1 - e^{-(t/R \cdot C)})$$

.

(4)

affected by the number of conducting power transistors, which can change dramatically in responding to large load changes, the actual *R* value in real circuits often exhibits large changes in LDO output settling process. This section enhances the early model by considering such changes on *R* value. In the following discussion, we use R(t) to denote the equivalent on-resistance of the power device array. For a digital LDO circuit with relatively high input voltage, e.g.  $V_{DD} \ge 0.7 \text{ V}$  [4, 5, 8], the conducting power devices typically operate in linear region and hence these devices can be treated as resistors and the equivalent on-resistance can be estimated as

$$R(t) = \frac{V_{\rm DD} - V_{\rm out}(t)}{I_{\rm in}(t)} \tag{6}$$

However, when the LDO is operating with a very low input voltage [3, 6, 9], the conducting power devices are likely operating in saturation region. The output resistance of a single conducting power device is  $r_0 = (V_A/I_{PMOS})$ , where  $V_A$  is the Early voltage of the MOS device. Thus

$$R(t) = \frac{V_{\rm A}}{I_{\rm PMOS} \cdot N(t)} = \frac{V_{\rm A}}{I_{\rm in}}$$

(7)

where N(t) is the number of conducting power transistors. The two equations can be put into a uniformed format as

$$R(t) = \frac{V_{EQ}}{I_{\rm in}(t)} = \frac{V_{EQ}}{I_{\rm in} + i_{\rm in}(t)}$$

(8)

where  $V_{EQ} = V_{DD} - V_{out}$  when power devices operate in linear region; and  $V_{EQ} = V_A$  when power devices operate in saturation region. Note that  $I_{in}(t)$  is written as the sum of two terms in the above equation. The first term is the steady-state current before the transient response; the second term is the current deviation from the steady state during its transient response.

Substituting R(t) expression in (8) to (2), we obtain:

$$\frac{\mathrm{d}(v_{\mathrm{out}}(t))}{\mathrm{d}t} + v_{\mathrm{out}}(t) \left( \frac{I_{\mathrm{in}}}{V_{EQ} \cdot C} + \frac{i_{\mathrm{in}}(t)}{V_{EQ} \cdot C} \right) = \frac{i_{\mathrm{in}}(t) - i_{\mathrm{load}}(t)}{C} \tag{9}$$

Steps of solving this differential equation are provided in Appendix 1. The obtained  $V_{out}(t)$  expression is presented in (10). Clearly, this model considers the fact that the equivalent on-resistance of the power device array exhibits different values along the process of the LDO circuit adjusting the number of conducting devices. Since R(t) is affected differently by load current increase or decrease,  $sign(\Delta i_{load})$  is used in (10) to distinguish the two scenarios. If load current increases,  $sign(\Delta i_{load}) = 1$ ; otherwise  $sign(\Delta i_{load}) = -1$ . Similar to the piecewise analytical equation in [20], the expression in (10) can be used in a piecewise manner to numerically compute LDO transient responses following the steps discussed in [20]. Since the new model more precisely captures the equivalent onresistance of the power device array during the LDO transient responses, it is more accurate compared to the previous model in [20].

### 4 Modelling LDO transient responses to reference voltage change

Digital LDOs are often used in dynamic voltage scaling applications, where the output voltage is frequently changed [1, 2, 10] by varying LDO reference input  $V_{ref}$ . An important parameter that characterises the LDO transient response in such scenarios is rise time  $t_{rise}$ , which is defined as the time interval that the LDO output departures from its original level and reaches the new reference voltage level for the first time. Interestingly, the model developed in the previous section also applies to this situation. This is due to the fact that the LDO system relies on the same mechanism to respond the load current change or reference voltage change. For example, after a load current increase, the LDO output voltage drops below V<sub>ref</sub> and the LDO feedback loop starts to increase the number of conducting power transistors until the LDO output reaches  $V_{ref}$ . Similarly, after a reference voltage increase, the LDO output becomes smaller than  $V_{ref}$  and the LDO feedback loop responses similarly. To use the developed model numerically computing the LDO output waveform after reference voltage change  $\Delta V_{ref}$ , we need set  $\Delta i_{load} = 0$  and replace sign( $\Delta i_{load}$ ) by  $sign(\Delta V_{ref})$ , where  $sign(\Delta V_{ref}) = 1$  for voltage reference increase and sign( $\Delta V_{ref}$ ) = -1 for voltage reference decrease (see (10)). When  $\Delta V_{\text{ref}}$  is small, the  $v_{\text{out}}(t)$  expression given in (4) can be approximated by the third-order Taylor series expansion. Subsequently, equation  $v_{out}(t_{rise}) = \Delta V_{ref}$  can be simplified to:

$$a \cdot t_{\text{rise}}^3 + b \cdot t_{\text{rise}}^2 + d = 0 \tag{11}$$

where

$$a = \frac{X}{6 \cdot (R \cdot C)^3}, \quad b = -\frac{X}{2 \cdot (R \cdot C)^2}$$

$$d = -\Delta V_{\text{ref}}$$

(12)

Note that the expression of *X* is given in (5). The derivation of the above equation as well as steps to solve it is provided in Appendix 2. The obtained expression for  $t_{rise}$  is directly listed as follows:

$$t_{\rm rise} = \frac{-(b+a \cdot t_0) + ({\rm sign}(d))\sqrt{b^2 - 2 \cdot a \cdot b \cdot t_0 - 3 \cdot a^2 \cdot t_0^2}}{2 \cdot a} \quad (13)$$

where  $t_0$  is given in (35) in Appendix 2. This expression will be useful in the prediction of LDO output steady-state ripples as discussed in the next section.

### 5 Modelling LDO output steady-state ripple

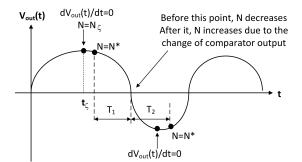

Even in the steady state, digital LDO output always exhibits small ripples, which become power supply noise for circuits powered by the LDO output. The steady-state ripples are caused by the finite control resolution of the discrete-time feedback loop. In this study, we use  $t_{\zeta}$  to represent the time that the LDO output voltage is at the peak or nadir of the ripples as shown in Fig. 5. In addition, we use  $N_{\zeta}$  to represent the number of conducting power devices at time  $t_{\zeta}$ ; and use  $N^*$  to represent the ideal N value such that the total current conducted by the power device array equals the load current. Since

$$\begin{aligned} v_{\text{out}}(t) &= V_{EQ} \Big( 1 - \mathrm{e}^{-(1/V_{EQ} \cdot C) \left( I_{\text{in}} \cdot t + \operatorname{sign}(\cdot \cdot i_{\text{load}}) \cdot I_{\text{PMOS}} \cdot f_{\text{clk}} \cdot (t^{2}/2) \right)} \\ &+ \sqrt{\frac{\pi \cdot V_{EQ}}{2 \cdot \operatorname{sign}(\cdot i_{\text{load}}) \cdot I_{\text{PMOS}} \cdot f_{\text{clk}} \cdot C}} \\ &\times \mathrm{e}^{-\left( (I_{\text{in}}^{2}/2 \cdot V_{EQ} \cdot C \cdot \operatorname{sign}(\times i_{\text{load}}) \cdot I_{\text{PMOS}} \cdot f_{\text{clk}}) + (1/V_{R0} \cdot C) \left( I_{\text{in}} \cdot t + \operatorname{sign}(\cdot i_{\text{load}}) \cdot I_{\text{PMOS}} \cdot f_{\text{clk}} \cdot (t^{2}/2) \right)} \right) \cdot (\Delta i_{\text{load}} + I_{\text{in}}) \end{aligned}$$

$$\begin{aligned} &\times \Big[ \mathrm{erfi} \Big( \frac{I_{RO}}{2 \cdot V_{EQ} \cdot C} \cdot \sqrt{\frac{2 \cdot V_{EQ} \cdot C}{\operatorname{sign}(\Delta i_{\text{load}}) \cdot I_{\text{PMOS}} \cdot f_{\text{clk}}}} \Big) \\ &- \mathrm{erfi} \Big( \frac{I_{\text{in}} + \operatorname{sign}(\Delta i_{\text{load}}) \cdot I_{\text{PMOS}} \cdot f_{\text{clk}} \cdot t}{2 \cdot V_{EQ} \cdot C} \cdot \sqrt{\frac{2 \cdot V_{EQ} \cdot C}{\operatorname{sign}(\Delta i_{\text{load}}) \cdot I_{\text{PMOS}} \cdot f_{\text{clk}}}} \Big) \Big] \end{aligned}$$

IET Circuits Devices Syst. © The Institution of Engineering and Technology 2018

Fig. 5 LDO output steady-state ripples

**Fig. 6** *Circuits used in LDO implementations* (*a*) Comparator used in LDO circuits, (*b*) Bi-directional shift register for LDO control

$(dv_{out}(t)/dt)|_{t=t_{\zeta}} = 0$ , there is no current charging or discharging capacitor C at time  $t_{\zeta}$ , referring to Fig. 3. From (2), we have:

$$v_{\text{out}}(t_{\zeta}) = (i_{\text{in}}(t_{\zeta}) - i_{\text{load}}) \cdot R = (N_{\zeta} - N^*) \cdot I_{\text{PMOS}} \cdot R$$

(14)

At the peak of the ripple, the LDO output is above the reference level and  $v_{out}(t_{\zeta}) > 0$ . Thus, (14) indicates  $N_{\zeta} > N^*$ . Similarly, at the nadir of the ripple,  $N_{\zeta} < N^*$ . Meanwhile, the N value always decreases during the time that the LDO output is above the reference level. This is because the LDO feedback loop is working on bringing the LDO output down to the reference level by reducing the number of conducting power devices. For a similar reason, the N value always increases when the LDO output is below the reference level. These observations lead to the conclusion that the peak or nadir always occur before  $N = N^*$  as shown in Fig. 5. In the figure, we also use  $T_1$  and  $T_2$  to denote the intervals between the times that the LDO control has the ideal  $N^*$ value and the time that the LDO output crosses the reference level, where the changing trend of N is reversed. Since the LDO control decreases or increases N at the same rate, we have  $T_1 = T_2$ . This implies that at the steady-state  $N_{\zeta}$  should be as close to  $N^*$  as possible. However, due to the finite control resolution,  $N_{\zeta}$  may not reach the exact  $N^*$  value (which may not be an integer) and hence

Table 1

Key design parameters of LDO circuits used in circuit simulation

| LDO circuits              | I        | II       | III      |

|---------------------------|----------|----------|----------|

| V <sub>DD</sub> , V       | 0.5      | 0.5      | 0.5      |

| power device (W/L)        | 0.4/0.12 | 0.8/0.12 | 1.2/0.12 |

| $f_{\rm clk},  {\rm MHz}$ | 2        | 2        | 2.5      |

| C <sub>load</sub> , nF    | 100      | 50       | 100      |

the maximum of  $N_{\zeta} - N^*$  is 1. Substituting this value to (14), we obtain the upper bound of the steady-state ripple magnitude:

$$V_{\text{RIPPLE}_{\text{MAX}}} = I_{\text{PMOS}} \cdot R \tag{15}$$

The LDO output behaviour starting from time  $t = t_{\zeta}$  is similar to the system response to a reference voltage change of  $V_{\text{RIPPLE}_{MAX}}$ . The duration from  $t = t_{\zeta}$  to the time that the LDO output reaches the reference level is  $t_{\text{rise}}$ . As illustrated in Fig. 5,  $t_{\text{rise}}$  is approximately one-quarter of the ripple period. Thus, we have:

$$f_{\text{RIPPLE}_{\text{MIN}}} = \frac{1}{4 \cdot t_{\text{rise}}(V_{\text{RIPPLE}_{\text{MAX}}})}$$

(16)

where  $t_{rise}(V_{RIPPLE_{MAX}})$  can be estimated using (13). Since the upper bound of the ripple magnitude is used in the above estimation, the obtained result should be the lower bound of the ripple frequency, noting that the larger the ripple magnitude is, the larger  $t_{rise}$  is.

### 6 Simulation results

To verify the accuracy of the derived models, three digital LDO circuits were designed using a 0.13  $\mu m$  CMOS technology. The designs use the topology in Fig. 1. The schematics of the comparator and control logic are depicted in Fig. 6. The control logic is similar to that in [3] and it consists of a 256-bit bidirectional shift register. Each bit of the shift register controls a power device. The left input of the shift register is tied to 0 and its right side input is connected to logic 1. If the comparator output is 1, indicating  $V_{\text{LDO}} < V_{\text{ref}}$ , the register shifts in 0's from it left input to turn on additional power devices; otherwise, the register shifts in 1's from its right input for turning off excessive power devices. For the convenience of discussion, the three designs are referred to as Designs I, II and III and their key design parameters are listed in Table 1. The designed LDO circuits were simulated using Cadence spectre tool with net lists generated from schematics. Since the LDO circuits operate with low clock frequencies and their output node capacitance is dominated by the large load capacitance, the schematic simulation should be reasonably accurate.

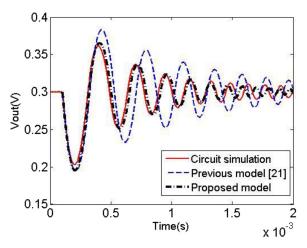

Fig. 7 shows the transient response of Design I when its load current is changed from 50 to 250  $\mu$ A at 100  $\mu$ s. The LDO reference input is 0.3 V in this case. The LDO output waveform obtained from circuit simulation is depicted by the solid line in the figure. The waveforms computed by the previous and proposed analytical models are shown by thin dash line and thick dash-dot line, respectively. Clearly, it shows that the analytical model developed in this work more accurately estimates the LDO transient response compared to the model in [20]. Additional circuit simulations with different load changes were also conducted for all the three LDO circuits with various  $V_{\rm ref}$  values. The maximum ripple voltages  $V_{\rm r,max}$  obtained from circuit simulation and estimated by the model developed in this work are compared in Table 2. It shows that the estimations from the proposed model are fairly close to the results from circuit simulations.

Circuit simulations were also conducted to investigate the accuracy of using the developed model to predict LDO transient responses after reference voltage changes. Table 3 compares the model estimations with results obtained from circuit simulation for rise time and the maximum overshoot voltage after LDO reference voltage changes. Note that the reference voltage of LDO Design II is switched from 0.45 to 0.35 V and hence its overshoot voltages have negative values, indicating that the LDO output will first go <0.35 V and then gradually settle at the reference level in its transient response. The comparison in Table 3 shows that the values estimated by the developed model and the results obtained from circuit simulations are reasonably close, which validates the claim that the developed model is also applicable to estimating digital LDO transient responses to voltage reference changes.

Circuit simulations were also conducted to examine the accuracy of the estimation equations for the steady-state output ripple magnitude and frequency. The LDO circuit used in this study

Fig. 7 Simulated and estimated transient response to load current change

has power transistor size as  $0.4 \,\mu$ m/ $0.12 \,\mu$ m. Different clock frequencies, load currents and output capacitance are selected in simulations to have four test cases as summarised in Table 4. As discussed in Section 5, the results from (15) and (16) are the upper bound of the ripple magnitude and lower bound of the ripple frequency, respectively. The comparisons in Table 4 confirm the above statements. To examine how load current affects steady-state behaviour, Test Cases I and II were selected such that they only differ by load current values. The comparison between the two shows that the ripple magnitude decreases with the increase of load current. Increased load current results in more conducting power devices and hence reduced *R* value. Therefore, the ripple magnitude is reduced as indicated in (15). The comparison also shows that the steady-state ripple frequency is increased with the increase of load current, which is mainly due to the decrease of

Table 2

Comparison of simulated and predicted maximum ripple voltage after load changes

| LDO circuits                 | I      | II      |         |  |  |  |  |

|------------------------------|--------|---------|---------|--|--|--|--|

| V <sub>ref</sub> , V         | 0.45   | 0.4     | 0.3     |  |  |  |  |

| I <sub>load</sub> change, μA | 75→150 | 100→300 | 100→600 |  |  |  |  |

| simulated $V_{r, max}, mV$   | 12.4   | 4.7     | 70.1    |  |  |  |  |

| predicted $V_{r, max}$ , mV  | 10.6   | 4.9     | 74.5    |  |  |  |  |

**Table 3** Comparison of simulated and predicted rise time and maximum overshoot voltage after  $V_{ref}$  change

| LDO circuits                     | I        | II        |          |  |  |  |

|----------------------------------|----------|-----------|----------|--|--|--|

| I <sub>load</sub> , μΑ           | 200      | 300       | 500      |  |  |  |

| $V_{\rm ref}$ change, V          | 0.3→0.35 | 0.45→0.35 | 0.35→0.4 |  |  |  |

| simulated $t_{rise}, \mu s$      | 61.3     | 61.1      | 27.1     |  |  |  |

| predicted $t_{rise}$ , $\mu s$   | 57.4     | 53.5      | 29.2     |  |  |  |

| simulated $V_{os}$ , mV          | 38.2     | -57.5     | 23.8     |  |  |  |

| predicted $V_{\rm os}, {\rm mV}$ | 38.6     | -57.4     | 29.8     |  |  |  |

Table 4

Comparison of simulated and predicted steadystate output ripple voltage and ripple frequency

| Test cases                                               |       | II    |       | IV   |

|----------------------------------------------------------|-------|-------|-------|------|

| V <sub>ref</sub> , mV                                    | 450   | 450   | 480   | 400  |

| $f_{\rm clk}, { m MHz}$                                  | 2     | 2     | 1     | 1    |

| C, nF                                                    | 100   | 100   | 50    | 50   |

| $I_{\text{load}}, \mu A$                                 | 50    | 200   | 100   | 100  |

| $V_{\text{RIPPLE}}$ , mV from simulation                 | 1.25  | 0.32  | 0.18  | 4.1  |

| predicted upper bound for $V_{\text{RIPPLE}}, \text{mV}$ | 1.3   | 0.33  | 0.2   | 7.3  |

| $f_{\text{RIPPLE}}$ , kHz from simulation                | 22.13 | 48.47 | 45.55 | 14.2 |

| predicted lower bound for $f_{\rm RIPPLE}, \rm kHz$      | 20.95 | 40.95 | 37.1  | 10.9 |

IET Circuits Devices Syst.

© The Institution of Engineering and Technology 2018

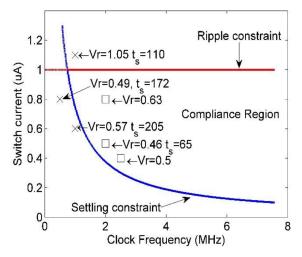

**Fig. 8** Design space partition to simultaneously satisfy steady-state ripple and settling time constraints

ripple voltage and hence reduced  $t_{rise}$  value. Test Cases III and IV only differ by their output voltage for examining the effect of the reference voltage on the steady-state behaviour. It shows that reducing the reference voltage increases the ripple magnitude and decreases the ripple frequency, which is mainly due to the increase of *R* at the LDO output node.

Finally, the derived models and estimation equations can be used to locate the ranges of key LDO design parameters for meeting the targeted transient performance. This helps designers effectively explore the design space at early design stage. The following illustrates how to use the developed models to partition the design space with multiple design constraints. It assumes that the LDO power supply, reference voltage, and load capacitance are selected as:  $V_{DD} = 0.5 \text{ V}$ ,  $V_{ref} = 0.45 \text{ V}$ , C = 200 nF. Also, the minimum LDO load current is expected to be 50  $\mu$ A in the targeted applications. The targeted performance specifications include: (i) the steady-state ripple magnitude should be smaller than 1 mV; (ii) after 50 µA load current change the LDO output settling time should be smaller than 150 µs with settling error  $V_{\epsilon} < 5 \text{ mV}$ . As discussed earlier, the steady-state ripple magnitude strongly depends on  $I_{PMOS}$ , the current conducted by a single power switch; the settling behaviour after load change is affected by both  $I_{PMOS}$ and clock frequency  $f_{\rm clk}$ . Thus, the design space in this example is a two-dimensional space with  $f_{\rm clk}$  and  $I_{\rm PMOS}$  as its horizontal and vertical axes as shown in Fig. 8.

When the LDO experiences the minimum load current, it has the largest output resistance R and hence the largest steady-state ripple magnitude. From the above selected design parameters, we know the LDO output resistance is 1 k $\Omega$  when it has the minimum load current. Thus, to satisfy the steady-state ripple magnitude requirement, the current of a single power switch should be smaller than 1 µA according to (15). This defines the ripple constraint boundary of the design space shown in Fig. 8. To satisfy the settling time requirement, the method discussed in our early work [20] was used to generate a curve that further partition the design space as shown in Fig. 8. To verify the obtained design space partition, six design configurations were simulated with using Cadence spectre tool. The three configurations located outside of the compliance region are indicated by symbol 'x' and the other three within the compliance region are represented by '[]'. The settling time and steady-state ripple magnitude measured from actual circuit simulations are listed beside the symbols. The units of the settling time and steady-state ripple magnitude are microsecond and millivolt, respectively. Due to limited space in the plot, the units are not displayed in the figure. Also, for two design configurations located in the compliance region, their maximum ripple voltages after load change are smaller than the error voltage used to determine settling time. Hence, they automatically satisfy the settling time requirement and their settling times are not displayed. These design cases and their circuit simulation results confirm the validity of the design space partition.

### Conclusion 7

This work develops analytical models and closed-form equations for estimating digital LDO transient performance as well as steadystate ripples. The accuracy of the developed models and equations is validated by comparing estimation results with data obtained from circuit simulations. The use of the estimation equations for design space exploration is also demonstrated in the paper. The developed models and equations can be integrated into design automation tools or directly used by designers to predict LDO transient performance at early design stage.

### 8 Acknowledgments

This research has been supported in part by grant NSF IIP 1535658 and the NSF I/UCRC for Embedded Systems at SIUC under grant NSF IIP 1361847. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the authors and do not necessarily reflect the views of the National Science Foundation.

#### References 9

- Kim, S.T., Shih, Y.-C., Mazumdar, K., et al.: 'Enabling wide autonomous [1] DVFS in a 22 nm graphics execution core using a digitally controlled hybrid LDO/switched-capacitor VR with fast droop mitigation'. Proc. Int. Solid-State Circuits Conf. (ISSCC), San Francisco, CA, February 2015, pp. 154-155

- Luria, K., Shor, J., Zelikson, M., et al.: 'Dual-use low-drop-out regulator/ power gate with linear and on-off conduction modes for microprocessor on-[2] die supply voltages in 14nm'. Proc. Int. Solid-State Circuits Conf. (ISSCC), San Francisco, CA, February 2015, pp. 156–157 Okama, Y., Ishida, K., Ryu, Y., *et al.*: '0.5-V input digital LDO with 98.7%

- [3] current efficiency and 2.7-µA quiescent current in 65 nm CMOS'. Proc.

- Custom Integrated Circuits Conf. (CICC), San Jose, 2010 Lee, Y.-H., Peng, S.-Y., Wu, A.C.-H., *et al.*: 'A 50 nA quiescent current asynchronous digital-LDO with PLL-modulated fast-DVS power [4] management in 40 nm CMOS for 5.6 times MIPS performance'. Proc. Symp. VLSI Circuits, Honolulu, HI, 2012, pp. 178-179

- Oh, T.J., Hwang, I.C.: 'A 110-nm CMOS 0.7-V input transient-enhanced digital low-dropout regulator with 99.98% current efficiency at 80-mA load', [5] IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 2015, 23, (7), pp. 1281-1286

- Raychowdhury, A., Somasekhar, D., Tschanz, J., et al.: 'A fully-digital phase-[6] locked low dropout regulator in 32 nm CMOS'. Proc. 2012 Symp. VLSI Circuits, Honolulu, HI, 2012, pp. 148-149

- [7] Yang, F., Mok, P.K.T.: 'A 0.6-1 V input capacitor-less asynchronous digital LDO with fast transient response achieving 9.5b over 500 mA loading range in 65-nm CMOS'. Proc. European Solid-State Circuits Conf. (ESSCIRC), Graz, 2015, pp. 180–183 Tai, C.L., Roth, A., Soenen, E.: 'A digital low drop-out regulator with wide

- [8] operating range in a 16 nm FinFET CMOS process'. Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC), Xiamen, 2015

- [9] Kim, Y., Li, P.: 'A 0.38 V near/sub-VT digitally controlled low-dropout regulator with enhanced power supply noise rejection in 90 nm CMOS process', *IET Circuits Dev. Syst.*, 2013, 7, (1), pp. 31–41 Peng, S.Y., Huang, T.-C., Lee, Y.-H., *et al.*: 'Instruction-cycle-based dynamic voltage scaling power management for low-power digital signal processor

- [10] with 53% power savings', IEEE J. Solid-State Circuits, 2013, 48, (11), pp. 2649-2661

- [11] Nasir, S.B., Gangopadhyay, S., Raychowdhury, A.: 'A 0.13 µm fully digital low-dropout regulator with adaptive control and reduced dynamic stability for ultra-wide dynamic range'. Proc. Int. Solid-State Circuits Conf. (ISSCC), San Francisco, CA, February 2015, pp. 98-99

- Chiu, C.C., Huang, P.-H., Lin, M., et al.: 'A 0.6 V resistance-locked loop [12] embedded digital low dropout regulator in 40 nm CMOS with 77% power supply rejection improvement'. Symp. VLSI Circuits Digest Technical

- Papers, June 2013, pp. 166–167 Gangopadhyay, S., Somasekhar, D., Tschanz, J.W., *et al.*: 'A 32 nm embedded, fully-digital, phase-locked low dropout regulator for fine grained power management in digital circuits', *IEEE J. Solid-State Circuits*, 2014, **49**, [13] (11), pp. 2684-2693

- Yang, F., Mok, P.K.T.: 'Fast-transient asynchronous digital LDO with load [14] regulation enhancement by soft multi-step switching and adaptive timing techniques in 65-nm CMOS'. 2015 IEEE Custom Integrated Circuits Conf. (CICC), San Jose, CA, 2015, pp. 1–4 Song, H., Rhee, W., Shim, I., *et al.*: 'Digital LDO with 1-bit  $\Delta\Sigma$  modulation

- [15] for low-voltage clock generation systems', Electron. Lett., 2016, 52, (25), pp. 2034-2036

- Kim, D., Seok, M.: '8.2 fully integrated low-drop-out regulator based on [16] event-driven PI control'. IEEE Int. Solid-State Circuits Conf. (ISSCC), San

- Francisco, CA, 2016, pp. 148–149 Lee, Y.J., Qu, W., Singh, S., *et al.*: 'A 200-mA digital low drop-out regulator with coarse-fine dual loop in mobile application processor', *IEEE J. Solid*-[17] State Circuits, 2017, 52, (1), pp. 64-76

- [18] Lee, B.: 'Technical review of low dropout voltage regulator operation and performance', Texas Instruments Application Note, 1999

- [19] Simrock, S.: 'Control theory'. Proc. CERN Accelerator School on Digital

- Signal Processing, 2007, pp. 73–130 Leitner, S., West, P., Lu, C., *et al.*: 'Digital LDO modeling for early design space exploration'. Proc. 29th IEEE Int. System on Chip Conf., Seattle, WA, [20] 6-9 September 2016, pp. 7-12

- Giustolisi, G., Palumbo, G., Spitale, E.: 'Robust miller compensation with [21] current amplifiers applied to LDO voltage regulators', IEEE Trans. Circuits Syst. I, 2012, 59, (9), pp. 1880-1893

- Ho, E.N.Y., Mok, P.K.T.: 'A capacitor-less CMOS active feedback low-dropout regulator with slew-rate enhancement for portable on-chip application', *IEEE Trans. Circuits Syst. II Express Briefs*, 2010, **57**, (2), pp. [22] 80-84

- [23] Wu, J., Boyer, A., Li, J., et al.: 'Modeling and simulation of LDO voltage regulator susceptibility to conducted EMI', IEEE Trans. Electromagn.

- Compat., 2014, **56**, (3), pp. 726-735 Pérez-Bailón, J., Márquez, A., Calvo, B., *et al.*: 'Fast-transient high-performance 0.18 µm CMOS LDO for battery-powered systems', *Electron. Lett.*, 2017, **53**, (8), pp. 551–552 Kim, D., Seok, M.: 'A fully integrated digital low-dropout regulator based on [24]

- [25] event-driven explicit time-coding architecture', IEEE J. Solid-State Circuits, 2017, 53, (11), pp. 3071-3080

#### Appendix 10

### 10.1 Appendix 1

This appendix provides the key steps of solving (9). Assume that there is a function  $\mu(t)$  satisfying (17) listed below. Multiplying both sides of (9) by  $\mu(t)$  results in a perfect derivative expression on the left hand side of the resultant equation. Thus with the help of  $\mu(t)$ , (9) can be solved by integration

$$\frac{\mathrm{d}(\mu(t))}{\mathrm{d}t} = \left(\frac{I_{RO}}{V_{EQ} \cdot C} + \frac{i_{\mathrm{in}}(t)}{V_{EQ} \cdot C}\right) \cdot \mu(t) \tag{17}$$

Using  $(1/\mu(t))(d(\mu(t))/dt) = (d/dt)\log|\mu(t)|$  and substituting (3) into (17) yields:

$$\int \frac{\mathrm{d}}{\mathrm{d}t} \log |\mu(t)| \mathrm{d}t = \int \frac{I_{RO}}{V_{EQ} \cdot C} + \frac{\operatorname{sign}(\Delta i_{\text{load}}) \cdot I_{\text{PMOS}} \cdot f_{\text{clk}} \cdot t}{V_{EQ} \cdot C} \mathrm{d}t \,(18)$$

In the above expression,  $sign(\Delta i_{load})$  is used to indicate if load current increases or decreases as discussed earlier.

Performing integration on both sides of (18) gives:

$$|\mu(t)| = e^{(1/V_{EQ} \cdot C) \left( I_{RO} \cdot t + \operatorname{sign}(\Delta i_{\text{load}}) \cdot I_{\text{PMOS}} \cdot f_{\text{clk}} \cdot (t^2/2) \right) + \operatorname{Constant}}$$

(19)

It can be further simplified to:

$$\mu(t) = \mathrm{e}^{(1/V_{EQ} \cdot C) \left( I_{RO} \cdot t + \mathrm{sign}(\Delta i_{\mathrm{load}}) \cdot I_{\mathrm{PMOS}} \cdot f_{\mathrm{clk}} \cdot (t^2/2) \right)}$$

(20)

Multiplying (9) by the obtained  $\mu(t)$  expression leads to (21). Introducing substitution terms given in (22) and integrating both sides of (21) yields the definite integral expressed in (23). Finally, evaluating the integral in the given interval and dividing it by  $e^{CA \cdot t + CB \cdot t^2}$  yields  $v_{out}(t)$  expression given in (24). Back substituting the terms in (22) leads to (10)

$$\frac{d\left(e^{(1/V_{EQ} \cdot C)(I_{RO} \cdot t + \operatorname{sign}(\Delta i_{\operatorname{load}}) \cdot I_{\operatorname{PMOS}} \cdot f_{\operatorname{clk}} \cdot (t^{2}/2))} \cdot v_{\operatorname{out}}(t)\right)}{dt} = e^{(1/V_{EQ} \cdot C)(I_{RO} \cdot t + \operatorname{sign}(\Delta i_{\operatorname{load}}) \cdot I_{\operatorname{PMOS}} \cdot f_{\operatorname{clk}} \cdot (t^{2}/2))} \cdot \frac{\dot{i}_{\operatorname{in}}(t) - i_{\operatorname{load}}(t)}{C}}{C}$$

(21)

$$CA = \frac{I_{RO}}{V_{EQ} \cdot C} \quad CB = \frac{\text{sign}(\Delta i_{\text{load}}) \cdot I_{\text{PMOS}} \cdot f_{\text{clk}}}{2 \cdot V_{EQ} \cdot C}$$

$$CC = \frac{\text{sign}(\Delta i_{\text{load}}) \cdot I_{\text{PMOS}} \cdot f_{\text{clk}}}{C} \quad CD = \frac{\Delta i_{\text{load}}}{C}$$

(22)

$${}^{+CB \cdot t^{2}} \cdot v_{\text{out}}(t) = \int_{0}^{t} e^{CA \cdot t + CB \cdot t^{2}} \cdot (CC \cdot t - CD) dt$$

$$= \frac{e^{-(CA^{2}/4 \cdot CB)}}{4 \cdot CB^{(3/2)}} \Big( 2 \cdot \sqrt{CB} \cdot CC \cdot e^{((CA + 2 \cdot CB \cdot t)^{2}/4 \cdot CB)} \quad (23)$$

$$-\sqrt{\pi} \cdot (CA \cdot CC + 2 \cdot CB \cdot CD) \cdot \operatorname{erfi}\left(\frac{CA + 2 \cdot CB}{2 \cdot \sqrt{C}}\right)$$

$$= \frac{CC}{2 \cdot CB} \Big( 1 - e^{-(CA \cdot t + CB \cdot t^{2})} \Big)$$

$$+ \frac{e^{-((CA + 2 \cdot CB \cdot t)^{2}/4 \cdot CB)}}{4 \cdot CB^{(3/2)}} \sqrt{\pi} \cdot (CA \cdot CC + 2 \cdot CB \cdot CD) \Big( \operatorname{erfi}\left(\frac{1}{2}(24)\right) \Big)$$

### 10.2 Appendix 2

$-\operatorname{erfi}\left(\frac{CA+2\cdot CB\cdot t}{2\cdot\sqrt{CB}}\right)\right)$

This appendix derives the third-order Taylor series expansion to approximate the LDO output trajectory. Express the third-order series expanded at t = 0 with unknown coefficients as

$$v_{\text{out}}(t) = a \cdot t^3 + b \cdot t^2 + c \cdot t \tag{25}$$

By definition of the expansion it follows that:

$$a = \frac{d^{3}(v_{\text{out}}(t))}{6 \cdot dt^{3}} \bigg|_{t=0} = \frac{X}{6 \cdot (R \cdot C)^{3}} \left( e^{-(t/R \cdot C)} \right) \bigg|_{t=0} = \frac{X}{6 \cdot (R \cdot C)^{3}} \quad (26)$$

$$b = \frac{d^2(v_{out}(t))}{2 \cdot dt^2} \bigg|_{t=0} = -\frac{X}{2 \cdot (R \cdot C)^2} \left( e^{-(t/R \cdot C)} \right) \bigg|_{t=0} = -\frac{X}{2 \cdot (R \cdot C)^2} (27)$$

$$c = \frac{d(v_{out}(t))}{dt}\Big|_{t=0} = Y + \frac{X}{R \cdot C} \left(e^{-(t/R \cdot C)}\right)\Big|_{t=0} = Y + \frac{X}{R \cdot C}$$

(28)

The LDO response to a reference voltage change is computed via (4) by setting  $\Delta i_{\text{load}}$  to zero. The rise time  $t_{\text{rise}}$  of the LDO output after a step change  $\Delta V_{\text{ref}}$  of the reference voltage can be approximated via  $v_{\text{out}}(t_{\text{rise}}) = \Delta V_{\text{ref}}$ . From (25), the rise time is one of the three roots of:

$$a \cdot t^3 + b \cdot t^2 + c \cdot t - \Delta V_{\text{ref}} = 0$$

<sup>(29)</sup>

Introducing notation  $d = -\Delta V_{\text{ref}}$  and noticing that c = 0 when  $\Delta i_{\text{load}} = 0$ , the above equation is written as

$$a \cdot t^{3} + b \cdot t^{2} + d = 0 \tag{30}$$

If the magnitude of d is not too large, (30) has three real roots. Thus an arbitrary solution of (30) may or may not be the rise time to  $\pm \Delta V_{\text{ref}}$ . For the special case where the linear term of a third degree polynomial equation is zero, the simplified cubic formula is given as

$$t_{0} = \sqrt[3]{\left(-\frac{b^{3}}{27 \cdot a^{3}} - \frac{d}{2 \cdot a}\right)} + \sqrt{\frac{b^{3} \cdot d}{27 \cdot a^{4}} + \frac{d^{2}}{4 \cdot a^{2}}} + \sqrt[3]{\left(-\frac{b^{3}}{27 \cdot a^{3}} - \frac{d}{2 \cdot a}\right)} - \sqrt{\frac{b^{3} \cdot d}{27 \cdot a^{4}} + \frac{d^{2}}{4 \cdot a^{2}}} - \frac{b}{3 \cdot a}$$

(31)

Also, within the domain of interest, the term under the square root is always negative. Thus with the substitutions:

$$A = \left(-\frac{b^3}{27 \cdot a^3} - \frac{d}{2 \cdot a}\right), \quad B = \sqrt{\left|\frac{b^3 \cdot d}{27 \cdot a^4} + \frac{d^2}{4 \cdot a^2}\right|}$$

(32)

Equation (31) can be simplified to:

$$t_0 = \sqrt[3]{A \pm B \cdot i} + \sqrt[3]{A \mp B \cdot i} - \frac{b}{3 \cdot a}$$

(33)

The complex result is then easily evaluated in polar form:

$$t_0 = \sqrt[6]{A^2 + B^2} \cdot \left( e^{\pm (i \cdot \arctan((B/A))/3)} + e^{\mp (i \cdot \arctan((B/A))/3)} \right) - \frac{b}{3 \cdot a}$$

(34)

As expected imaginary components cancel out in the equation. For the real component,  $\arctan(x)$  naturally only reveals one of two possible solutions, located in the first and fourth quadrants of the complex plane. The desired solution depends on the sign of A. If A > 0,  $\operatorname{sign}(A) = 1$  and the solution lies within quadrant one. However, if A < 0,  $\operatorname{sign}(A) = -1$  and  $\pi$  is added to the argument of the cosine function in (35), describing the solution in the third quadrant of the complex plane. (Due to the factor 1/3 resulting from the cubic root, the argument is still kept within the first quadrant.)

$$t_{0} = -\frac{b}{3 \cdot a} + 2 \cdot \sqrt[6]{A^{2} + B^{2}} \times \cdot \cos\left(\frac{\arctan((B/A)) + \pi((1 - \operatorname{sign}(A)/2))}{3}\right)$$

(35)

As mentioned earlier, in the domain of interest there exist three real roots, two of which are positive.  $t_0$  in (35) yields the positive root not corresponding to the rise time of the LDO output. Since  $t_0$  is a root of (30),  $(t - t_0)$  must be a factor of (30). Performing polynomial division gives the second-order polynomial:

$$a \cdot t_{\text{RISE}}^{2} + (b + a \cdot t_{0}) \cdot t_{\text{RISE}} + (b + a \cdot t_{0}) \cdot t_{0} = 0$$

(36)

Finally, the positive root of (36) corresponds to the rise time of the LDO output to  $\pm \Delta V_{ref}$ . Its solution is given explicitly in (13).