# Southern Illinois University Carbondale **OpenSIUC**

Articles

Department of Electrical and Computer Engineering

Winter 4-1-2016

## Effects of Deposition Process on Poly-Si Microscale Energy Harvesting Systems: A Simulation Study

Elif Selin Mungan

Purdue University, ebaytok@purdue.edu

Chao Lu Southern Illinois University Carbondale, lu43@purdue.edu

Chih-Hisang Ho

Purdue University, ho7@purdue.edu

Kaushik Roy Purdue University, kaushik@purdue.edu

Follow this and additional works at: http://opensiuc.lib.siu.edu/ece articles

#### Recommended Citation

Mungan, Elif S., Lu, Chao, Ho, Chih-Hisang and Roy, Kaushik. "Effects of Deposition Process on Poly-Si Microscale Energy Harvesting Systems: A Simulation Study." *IEEE TRANSACTIONS ON ELECTRON DEVICES* 63, No. 4 (Winter 2016): 1650-1657.

This Article is brought to you for free and open access by the Department of Electrical and Computer Engineering at OpenSIUC. It has been accepted for inclusion in Articles by an authorized administrator of OpenSIUC. For more information, please contact opensiuc@lib.siu.edu.

### Effects of Deposition Process on Poly-Si Micro-scale Energy Scavenging Systems

Elif S. Mungan, Chao Lu, Chih-Hsiang Ho and Kaushik Roy, Fellow, IEEE

Abstract— In this paper, the feasibility of a low temperature polysilicon (LTPS) micro-scale energy harvester for a wireless sensor node is investigated. For that purpose, two device level models for the LTPS solar cell and thin film transistors (TFTs) are proposed and employed in system level evaluation of an energy harvesting system. The results of our analysis indicate that (i) the maximum power operating point for the solar cell is different when connected to a lossy power converter, (ii) increasing the average grain size (GrS) of the LTPS film can reduce the circuit area by 20 times while increasing the output power by 6%, (iii) the performance of the wireless sensor node is limited by the TFT performance for an LTPS process with high trap density (NT).

*Index Terms*— energy harvesting, grain boundaries, numerical simulations, optimization, photovoltaic cells, statistical analysis, thin film transistors.

#### I. INTRODUCTION

$\mathbf{F}^{\mathrm{ROM}}$  patient monitoring [1] to agricultural management [2] or space weather visualization [3] to assessing the condition of a bridge [4], many applications call for self-sufficient systems when battery replacement is not a favorable option. These systems can be implemented with wireless sensor networks which are created by deploying a vast number of sensors that communicate with a central processor making the decisions. To achieve self-sufficiency, the wireless sensor networks are required to harvest energy such as solar, thermal, piezoelectric or radio-frequency energies which are readily available in the ambient environment [5]. Among these available sources, solar energy is the most promising one due to its high power density -- in the mW/cm² range for outdoor, and in the  $\mu$ W/cm² range for indoor applications [6].

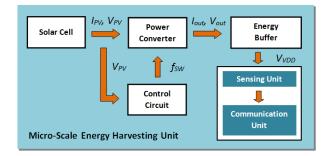

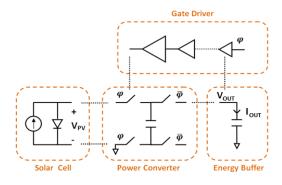

In a wireless sensor node as illustrated in Fig. 1, the power consumed by the sensing and communication units are provided by the micro-scale energy harvesting unit that utilizes a solar cell as the energy source. Due to the low output voltage of the solar cell  $(V_{PV})$ , it needs to be converted to the required system voltage  $(V_{VDD})$  to operate the sensors and transmit the obtained data to the central processor. This conversion is handled by a DC-DC power converter whose switching frequency  $(f_{SW})$  is determined by a control circuitry

Manuscript received April 20, 2015. This work was funded by National Science Foundation (NSF)

E. S. Mungan, C. Lu, C. Ho and K. Roy are with the School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47906 USA (e-mail:ebaytok@purdue.edu; lu43@purdue.edu; ho7@purdue.edu; kaushik@purdue.edu).

Fig. 1 Signal flow between the operating units of a wireless sensor node

that makes sure the solar cell is biased at the optimum operating point under different light intensities. The harvested energy is stored in energy buffer that can be a rechargeable battery or a supercapacitor.

Since wireless sensor networks employ large numbers of sensor nodes, the nodes are required to be compact, low cost and consume low power. The cost of an integrated circuit can be reduced by reducing the thermal budget of the deposition process. Hence, unlike the conventional approach, in this work the micro-scale energy harvester is envisioned to be integrated on a glass substrate using low temperature polysilicon (LTPS) technology. On the other hand, reducing the thermal budget causes the deposited materials to be polycrystalline (poly). These materials are composed of crystalline regions with different orientations (grains) and defective regions where the grains meet (grain boundaries (GBs)). The traps along GBs degrade the performance of the devices fabricated with this process and therefore introduce trade-offs for the system design in terms of system area, speed and power consumption. This degradation, however, can be tolerated for wireless sensor networks since the duty cycles can be around 1% [6].

The aim of this work is to make sure that the *LTPS* process can be used to fabricate the wireless sensor node in Fig. 1 despite the degradation due to *GBs*. To achieve this goal, one should be able to model the implications of *GBs* on the performance of the fundamental building blocks of the system. For this purpose, device level models are proposed for the polysilicon solar cell and thin film transistor (*TFT*), which are the building blocks of the proposed energy source and integrated circuits, respectively. Using compact models, the performance of the proposed devices are assessed at the circuit level and the overall system is optimized as the solar cell array and the power conditioning units are co-optimized. By

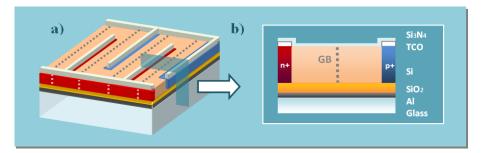

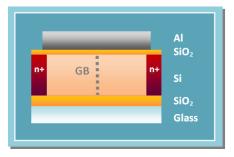

Fig. 2 The top view of (a) the proposed solar cell and (b) the cross-section of the simulated device.

following this holistic approach, the effects of process parameters namely silicon thickness  $(t_{Si})$ , average grain size (GrS) and GB trap density  $(N_T)$  on the performance of these devices, circuits and the system are investigated. Unlike the conventional approach, our holistic approach provides more insight, gives more control over the process and indicates the design tradeoffs that are not visible when each building block is studied in isolation.

The rest of this paper is organized as follows: the devicelevel model proposed for the LTPS solar cell is discussed in Section II, followed by the model for the *LTPS TFT* in Section III. The performance of the TFT model is assessed in a power converter circuit in Section IV. The building blocks of a wireless sensor network (the energy source, the power converter and the peripheral circuitry) are put together to study the system performance and sensitivity to process parameters in Section V. Finally, the conclusions are drawn in Section VI.

#### II. SOLAR CELL MODELING

As the power source of the system on glass, the solar cell device structure in Fig. 2.b was proposed previously in [7]. Since the aim of this work is to use the same process technology for the solar cell and TFTs used for the power converter and application units, the range for  $t_{Si}$  is kept below 1 µm. Using a classical device structure in which anode and cathode are placed on top and bottom of the cell would be problematic for thin devices since it could have caused shunting problem during contact formation [8]. Therefore, the proposed cell structure is kept similar to a TFT as it can be seen from Fig. 2b.

Previously in [7], the distance between n+ and p+ doped Si regions ( $W_{SC}$ ) was assumed to be equal to the GrS of a process such that the maximum number of GBs in the channel is limited to one. This requires very short  $W_{SC}$ s which increases the process complexity and cost. To study the trade-off between performance and cost, the solar cell model in [7] is improved such that it can simulate device structures with multiple GBs,  $W_{SC}$ s and  $t_{Si}$ s in a faster fashion. This is achieved by solving 1D drift-diffusion equations using the Newton's iteration scheme for the structure in Fig. 2b [9].

The optical generation profiles used to model solar cells with different  $t_{Si}$ s were reported in [10]. GBs are modeled as 4nm-wide regions with  $N_T$  and the energy levels indicated in

TABLE I SOLAR CELL DEVICE PARAMETERS

| Parameter                   | Value                                                                   |  |  |

|-----------------------------|-------------------------------------------------------------------------|--|--|

| $N_{D+}$ , $N_A$ , $N_{A+}$ | 10 <sup>18</sup> , 10 <sup>15</sup> , 10 <sup>18</sup> cm <sup>-3</sup> |  |  |

| $W_{SC}$                    | 0.2 -0.8 μm                                                             |  |  |

| $W_{CNT}$                   | 50 nm                                                                   |  |  |

| $t_{Si}$                    | 0.2 -0.8 μm                                                             |  |  |

| tsi3N4, tsi02               | 46 nm, 50 nm                                                            |  |  |

Doping concentrations for n+, p, p+ regions  $(N_{D+}, N_A, N_{A+})$ , width of p region  $(W_{SC})$ , width of contact region  $(W_{CNT})$ ; Si,  $Si_3N_4$ , $SiO_2$  thicknesses ( $t_{Si.}$   $t_{Si3N4.}$   $t_{SiO2}$ ).

[11]. Furthermore, GBs are assumed to be unidirectional and orthogonal to the current flow while the illumination is assumed to be at standard terrestrial conditions (AM 1.5) [12].

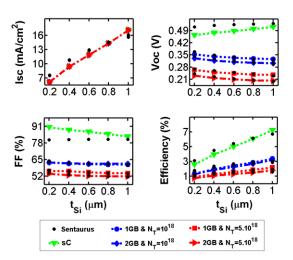

The results of our analysis are compared with 2D simulation results obtained for the same structure in a commercial driftdiffusion solver, Sentaurus [13]. The short circuit current ( $I_{SC}$ ), open circuit voltage  $(V_{OC})$ , fill factor (FF) and conversion efficiency of a  $W_{SC} = 0.2 \mu m$  solar cell are calculated for cases when there is: (a) no GB (hence the material is singlecrystalline (sC)), (b) one GB placed  $W_{SC}/4$  distance away from the n+ region (1GB) and (c) when there are two GBs, each placed  $W_{SC}$  /4 distance away from the n+ and p+ regions,

Fig. 3 2D Sentaurus results ( ) vs 1D simulation results when there is (a) no *GB* ( $^{\bullet}\nabla^{\bullet}$ ), (**b**) there is one *GB* with  $N_T = 10^{18} \text{cm}^{-3}(^{\bullet}\bullet^{\bullet})$ , (**c**) there are two GBs with  $N_T = 10^{18} \text{cm}^{-3}$  (d) there is one GB with  $N_T = 5 \times 10^{18} \text{cm}^{-3}$ ), (e) there are two GBs with  $N_T = 5 \times 10^{-18} \text{cm}^{-3}(\ )$  within a single device.

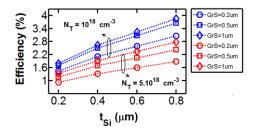

Fig. 4 Efficiency values of 1 cm<sup>2</sup> solar cells simulated for processes with different average grain sizes (GrSs) and GB trap densities ( $N_Ts$ ).

respectively (2GB). As shown in Fig. 3, although there are slight mismatches due to 2D effects, results of the proposed model match well with Sentaurus results overall. Another observation from Fig. 3 is the rapid reduction in efficiency with the presence of a single GB even though the  $N_T$  is low. On the other hand, introducing a second GB does not reduce the efficiency dramatically.

Once the proposed 1D micro-scale solar cell model is calibrated, the performance of a 1 cm<sup>2</sup> solar cell is simulated. For this purpose, 100 unit cells with  $W_{SC} = 0.2 \,\mu m$  and random number of GBs at random locations are simulated. Afterwards, their SPICE models are connected in parallel to make up a 1 cm<sup>2</sup> solar cell. The GBs in these devices are placed based on the lognormal distribution with average GrSs of 0.2, 0.5 and 1 µm and a standard deviation of 0.4 µm. The contact sheet resistances between these unit cells are neglected and the results are plotted in Fig. 4. Here, it can be observed that the efficiencies of 1 cm<sup>2</sup> cells for GrS = 0.2 µm and  $N_T = 5 \times 10^{-18}$ cm<sup>-3</sup> are similar to the efficiencies of *poly* cells (1GB or 2GB) with the same  $N_T$  in Fig. 3. The efficiency of a 1 cm<sup>2</sup> cell improves with the GrS, especially for thicker samples. Yet, the efficiency values remain lower than the sC results in Fig. 3. This trend occurs due to the unit cells with one or more GBs which sink the current in an exponential fashion. These defective unit cells dominate the 1 cm<sup>2</sup> cell's efficiency even though the probability of having a GB within a unit cell decreases significantly for larger GrSs.

#### III. THIN FILM TRANSISTOR MODELING

To realize a polysilicon based wireless sensor node, the transistors are modeled with the same process used for the energy source. The authors previously proposed a narrow channel polysilicon TFT for digital [11] and analog [14] applications. Aiming for good performance in both applications, the 2D TFT model in Fig. 5 is designed with the parameters in Table II in Sentaurus. Similar to the solar cell, the GBs in the TFTs are assumed to be unidirectional and perpendicular to the current flow. They also have the same  $N_{TS}$  and trap energy levels. The gate oxide thickness is determined such that the p-type TFT (pTFT) could be operated at the supply voltage required by the sensing and communication

Fig. 5 Cross-section of the simulated nTFT

#### TABLE II TFT Device Parameters

| Parameter             | Value                             |  |  |

|-----------------------|-----------------------------------|--|--|

| $L_{CH}$              | 500 nm                            |  |  |

| $t_{Si}$ , $t_{SiO2}$ | 50 nm, 15 nm                      |  |  |

| $N_S$ , $N_D$         | $10^{20} \text{ cm}^{-3}$         |  |  |

| $N_{Dbody}$           | $10^{15} \text{ cm}^{-3}$         |  |  |

| $N_{Abody}$           | 10 <sup>17</sup> cm <sup>-3</sup> |  |  |

Channel Length ( $L_{CH}$ ), Si and SiO<sub>2</sub> thicknesses ( $t_{Si}$ ,  $t_{SiO2}$ ), doping concentrations for source and drain regions ( $N_S$ ,  $N_D$ ), pTFT Body Doping ( $N_{Dbody}$ ), nTFT Body Doping ( $N_{Abody}$ ).

TABLE III

THRESHOLD VOLTAGES USED FOR TFT SPICE MODELS

|      | sC     | $N_T=10^{18}cm^{\text{-}3}$ | $N_T  = 5x10^{18} \; cm^{\text{-}3}$ |

|------|--------|-----------------------------|--------------------------------------|

| nTFT | 0.14 V | 0.22 V                      | 0.67 V                               |

| pTFT | 0.75 V | 0.87 V                      | 1.54 V                               |

units. Since the energy harvesting unit is targeted to power a sensing unit similar to the commercially available TELOS wireless sensing node [15], the supply voltage is chosen to be 2.4 V and oxide thickness is scaled down to 15 nm.

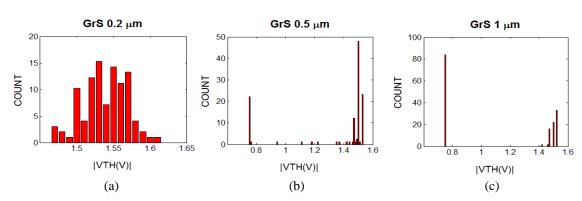

With the model in hand, the variation in threshold voltage  $(V_{TH})$  due to the number and  $N_T$  of GBs are studied. To do that, GBs are placed randomly based on the lognormal distributions used for solar cells and 100 TFT samples with a channel length  $(L_{CH})$  of 0.5  $\mu$ m are simulated. Due to the Aluminum metal work function of the gate, the  $V_{TH}$  of pTFT is found to be much higher than that of nTFT.

Fig. 6 Threshold voltage distributions of pTFTs simulated for the processes with  $N_T = 5 \times 10^{-18} \text{cm}^{-3}$  and average grain sizes (GrSs) of 0.2, 0.5 and 1  $\mu$ m

It is clear from Fig. 6 that if GrS of the process is comparable to  $L_{CH}$  (as in Fig. 6.b), the TFTs might be sC and  $V_{TH}$  of the devices is far smaller than its poly counterparts. As the GrS is increased (from Fig. 6a to Fig 6c), the variation in  $V_{TH}$  values gets larger. For the process in Fig. 6b, the difference in  $V_{TH}$  values is found to be  $\sim 0.7$ V and 4 significant peaks are observed. These peaks indicate 4 different distributions for cases when: (a) the device is sC, (b) there is 1 GB where the GB occurs at a non-critical position (close to the drain region), (c) there is 1 GB occurring at a critical position (close to the source region) and (d) there are two or more GBs occurring in the device. This wide variation can be avoided by increasing the GrS (e.g. to 1  $\mu$ m) so that the probability of having sC case is more likely as shown in Fig. 6c.

To do circuit simulations, two SPICE models are created: one for the sC TFTs (case a (explained above)) and another for the poly TFTs (cases b, c and d) using the level 62 RPI TFT model [16]. For the poly case, a representative device is chosen by making a boxplot of the simulated  $V_{TH}$  values and picking the device with mean  $V_{TH}$  value. The poly SPICE model is designed for the process with GrS = 0.2  $\mu m$ . The model is kept the same across different GrSs, since the mean  $V_{TH}$  does not change significantly with respect to GrSs (maximum deviation from the mean  $V_{TH}$  of the GrS = 0.2  $\mu m$  case is found to be 8%). Obtained  $V_{TH}ss$  are reported in Table III, which indicates that the circuit as well as the system performance will be limited by the performance of the pTFT.

#### IV. POWER CONVERTER DESIGN

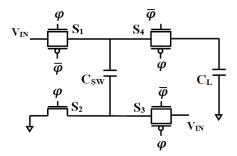

As previously stated in Section III, the system supply voltage requirement for the wireless sensor node under consideration is 2.4 V. Given that the  $V_{OC}$  of a single-junction solar cell is less than 0.5 V (as in Fig. 3), the output voltage of the solar cell needs to be converted to 2.4 V. Without loss of generality, the charge pump topology in Fig. 7 is used for this purpose. In this topology, switching capacitance ( $C_{SW}$ ) is charged via S1 and S2 switches during  $\varphi$  phase of the clock. On the other hand, during the  $\bar{\varphi}$  phase,  $C_{SW}$  is charged from the reverse direction by S3 and S4, leading to a voltage increase on both nodes of the capacitance. Again during  $\bar{\varphi}$ , the charge stored in  $C_{SW}$  is transferred to the next stage. For the single-stage charge pump in Fig. 7, this charge is transferred to the load capacitance ( $C_L$ ).

Assuming ideal switches and capacitors, one can calculate the output current transferred to the load to be [17]:

$$I_{OUT} = \frac{f_{SW}c_{SW}}{N} \left[ (N+1)V_{IN} - V_{OUT} \right] \tag{1} \label{eq:out}$$

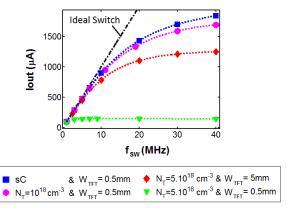

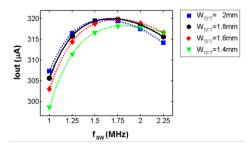

where  $f_{SW}$  is the clock frequency controlling the switches, N is the number of power converter stages,  $V_{IN}$  is the source voltage and  $V_{OUT}$  is the voltage at the output.  $I_{OUT}$  is determined by the equivalent resistance of switching capacitance ( $R_{CSW}$ ). Note that,  $I_{OUT}$  is linearly proportional to  $f_{SW}$  as shown in Fig. 8. On the other hand, unlike ideal switches, TFT switches have finite on resistances ( $R_{ON}$ s)

Fig. 7 Single-stage linear charge pump schematic

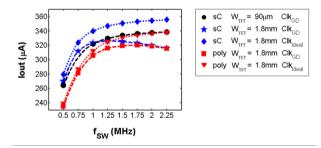

Fig. 8 Output current of a single-stage charge pump for an ideal switch, and TFTs with different widths ( $W_{TFT}$ s) and trap densities ( $N_T$ s).

which become comparable to  $R_{CSW}$  at high frequencies. This change in dominant resistive element causes the plateau observed for  $I_{OUT}$  at high frequencies (see Fig. 8) which is described as the fast switching limit in literature [18]. In this study, the frequency for which  $I_{OUT}$  deviates from the ideal switch behavior by 10% is defined as the knee frequency ( $f_K$ ).

For the switches modeled with the TFT model with  $N_T = 5 \times 10^{18}$  cm<sup>-3</sup> (high  $N_T$ ) and  $L_{CH} = 0.5$  mm,  $f_K$  occurs at 1 MHz. To reduce  $R_{ON}$ , TFT width ( $W_{TFT}$ ) can be increased (e.g. to 5 mm) with a corresponding increase in  $f_K$  (to 4.6 MHz). Yet, as the switches get larger so do the gate capacitances of TFTs and the switching loss due to charging and discharging of these capacitances. In addition to the switching loss, the circuit would be more prone to clock feedthrough problem [19]. Therefore, there is a limit to the improvement in  $f_K$  that can be obtained by increasing  $W_{TFT}$ . Another way of improving  $f_K$  would be to reduce  $N_T$  (e.g. to  $10^{18}$  cm<sup>-3</sup>), leading to an  $f_K$  of 8.9 MHz, which is very similar to the sC case with an  $f_K$  of 9.6 MHz.

#### V. ENERGY SCAVENGING SYSTEM DESIGN

### A. System Optimization

To study the effects of process conditions on wireless sensor nodes, the building blocks modeled in the previous sections are put together as shown in Fig. 9. The solar cell as the energy source is represented with its SPICE model. Note, the series and the shunt resistances are not taken into account due to the small size of the cell. The solar cell output voltage is provided at the input of the single-stage power converter

and converted to 2.4 V ( $V_{OUT}$ ). By selecting lower number of stages for the power converter, the number of switches and the switching loss are minimized. The harvested energy is stored in  $C_L$  which acts as the energy buffer. An inverter chain is designed to drive the gates of the TFT switches in the power converter and estimate the switching loss. Previously, the control unit that regulates the  $f_{SW}$  and the input resistance of the power converter was implemented with a voltage controlled oscillator (VCO) and a driver [20]. Since the power consumption of the VCO was negligible with respect to the switching loss, it is omitted in this analysis. Therefore, the initial clock signal ( $\varphi$ ) is provided by an ideal voltage source. In addition to that, the supply voltage of the gate driver is provided by the energy buffer. Thus, the net system  $I_{OUT}$  is obtained to be less than what is harvested from the solar cell.

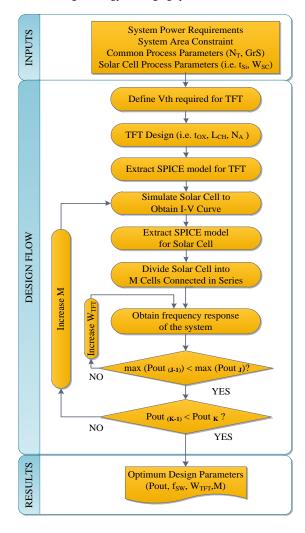

To optimize the performance of the system in Fig. 9, the design flow in Fig. 10 is employed. Before starting the design, the power and area requirements for the system are determined. The system is investigated for the three processes whose parameters are shown in Table IV. From these parameters,  $N_T$  and GrS are common for both solar cell and TFTs while  $t_{Si}$  and  $W_{SC}$  are solar cell specific. The results for these three processes are compared to demonstrate the change in system performance with respect to process conditions.

TABLE IV

PROCESS PARAMETERS CONSIDERED IN THE SYSTEM ANALYSIS

|         | $N_T$ (cm <sup>-3</sup> ) | GrS (µm) | $t_{Si}\ (\mu m)$ | $W_{SC}(\mu m)$ |

|---------|---------------------------|----------|-------------------|-----------------|

| Worst   | 5x10 <sup>18</sup>        | 0.2      | 0.2               | 0.2             |

| Average | $5x10^{18}$               | 1        | 0.8               | 0.2             |

| Best    | $1x10^{18}$               | 1        | 0.8               | 0.2             |

The design process is initiated with determining the maximum  $V_{TH}$  required by the power converter. Based on this criterion, the TFT is designed with the model explained in Section III, whereas the solar cell is modeled as in Section II. Afterwards, the 1 cm<sup>2</sup> solar cell is divided into M regions that are connected in series. Finally, to optimize the system performance, system output power ( $P_{OUT}$ ) is monitored for different solar cell array configurations. For each configuration, the  $W_{TFT}$  is optimized while the gate driver is scaled accordingly. Note that, this framework gives the user multiple options to improve the system performance. One can improve solar cell process parameters, redesign TFT for a better performance or optimize number of power converter stages to improve the  $P_{OUT}$  if system requirements are not met.

The results for the  $W_{TFT}$  optimization for the "Worst" process with M=7 is shown in Fig. 11. The results indicate an optimum  $W_{TFT}$  for the best system performance. For a small  $W_{TFT}$  (e.g. 1.4 mm)  $R_{ON}$  of the transistor is high and the transistor cannot provide the required current at that range of frequency. On the other hand, for large  $W_{TFT}$ , e.g. 2 mm, the switching loss at the gate driver manifests itself at higher frequencies since it is linearly proportional to  $f_{SW}$  ( $P_{SW} = CV_{DD}^2f$ ). The optimum  $W_{TFT}$  is observed to be 1.8 mm, with the system operating at 1.75 MHz to provide the best

Fig. 9 Energy scavenging system schematic

Fig. 10 Bottom-up design flow for the micro-scale energy harvesting system in Fig. 9.

performance.

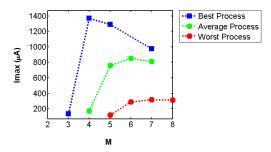

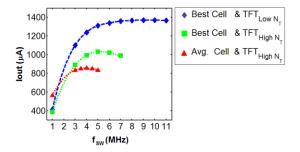

This study is extended for different processes and different Ms. The maximum net  $I_{OUT}s$  for each M ( $I_{MAX}s$ ) are reported in Fig. 12. The results show that the optimum Ms for the cells fabricated with the 'Best', 'Average' and the 'Worst' case processes in the design space are 4, 6, and 7 respectively. For Ms smaller than the optimum ones, the maximum current that the solar cell can provide is high. Hence, the power converter

Fig. 11 TFT width optimization for worst process condition

Fig. 12 Solar cell array optimization for different process conditions. [number of cells connected in series (M)]

needs to operate at high frequencies with higher switching loss. Besides, the converter might be operating close to or beyond its  $f_K$  which would again limit  $I_{OUT}$ . Therefore,  $I_{OUT}$  obtained at a lower frequency would provide better results. In such a case, the maximum operating point of the solar cell when it is isolated from the system  $(V_{MAX}, I_{MAX})$  is different than its optimum operating point when it is connected to the system  $(V_{SYS}, I_{SYS})$ . For Ms higher than the optimum value,  $I_{MAX}$  scales down while  $V_{MAX}$  increases. However, due to lower overdrive voltages for nTFT and asymmetric performance of nTFT and pTFT, the input resistance of the power converter also increases with  $V_{IN}$ . Hence, the system  $I_{OUT}$  reduces.

Finally, the power conversion efficiency is also found to be changing with process parameters. For the "Best" process with M=4, the power conversion efficiency of the converter is found to be 89% while it is observed to be 86% and 78% for the "Average" process with M=6 and the "Worst" process with M=7.

#### B. Effect of Process on the System Performance

When the maximum  $I_{MAX}$  values for the "Best", "Average" and "Worst" cases in Fig. 12 are compared, a significant change can be observed. This change roots both from the change in the solar cell and TFT performance with the changes in the process. In this subsection, the contribution of each device is quantified and how the process parameters change the overall system performance is studied.

#### 1) Effects of GrS on the System Performance

For the "Worst" process, if GrS of the process increases from 0.2  $\mu$ m to 1  $\mu$ m, the probability of having no GB in the

Fig. 13 System performance improvement due to increase in the *GrS* and improved *TFT* performance. [single-crystalline (*sC*), polycrystalline (*poly*), clocks provided by gate drivers (Clk<sub>GD</sub>) or by ideal voltage sources (Clk<sub>ideal</sub>)]

Fig. 14 System performance improvement when the fabrication process is changed from "Average" to the "Best" cases in Table IV.

device increases significantly (see Fig. 6). Provided GrS is fixed for the solar cell model, the improvement in the system performance would be solely due to the improvement in TFT and the power converter performance. To study this improvement, the system is designed both with sC and poly TFTs driven by ideal clocks (Clkideal case). The results in Fig. 13 indicate that the output current can increase slightly (by 20 μA) if the TFT model is switched from the poly model with high  $N_T$  to sC one. In the next stage, the switching power loss is taken into account by implementing gate drivers ( $Clk_{GD}$ ) case) with same sized sC and poly TFTs. Since sC TFTs can conduct more current, they lose more power while switching the gates. Hence, in this iso-area comparison, net  $I_{OUT}$  of the system is observed to be improving only by 6 µW. On the other hand, if an iso-performance comparison was conducted, the improvement in net  $I_{OUT}$  would be more significant. When ideal clocks are used to drive the gates,  $W_{TFT}$  of the sC device can be scaled down to 90  $\mu$ m to provide the same  $I_{OUT}$  as the poly TFT with  $W_{TFT}$  of 1.8 mm. In this scenario, besides 20 times reduction in the circuit area, the gate driver can also be scaled down to reduce the switching power loss. Thus, the system  $I_{OUT}$  can be improved by 18  $\mu$ A and the output power increases by 6%.

#### 2) Effects of $N_T$ on the System Performance

As a second case study, the fabrication process is changed from the "Average" to the "Best" process. If the solar cells are studied in isolation, the output powers of the cell arrays are found to improve by  $1082 \mu W$ . When both the "Average" and "Best" solar cells are interfaced with the power converter employing the *poly TFT* model with high  $N_T$ ,  $I_{OUT}$  frequency response would change from the red triangle curve in Fig. 14

to the green square curve and the improvement would reduce to 355  $\mu$ W. On the other hand, when the system is actually fabricated, the "Best" cell would be interfaced with a power converter employing the low  $N_T$  TFT model (see Table IV). Therefore, the system's actual  $I_{OUT}$  is the blue diamond curve in Fig. 14. Once the TFT model is changed, the output power of the system fabricated with the "Best" solar cell improves by 867  $\mu$ W. Hence, the system output power improves by 1222  $\mu$ W when the process is changed from the "Average" to the "Best". These results indicate that the solar cell output power can increase significantly. Yet, the net harvested power is going to be limited by the TFT performance.

#### VI. CONCLUSION

In this paper, a bottom-up modeling approach is applied to study the performance of an integrated LTPS micro-scale energy harvesting system. At device level, solar cell performance is found to reduce sharply with introduction of  $N_T$  unlike TFTs. On the other hand, a significant variation in TFT performance is observed for small  $L_{CH}$ , which can be kept under control by obtaining larger GrS. At the circuit level, the operation frequencies (and therefore the maximum  $I_{OUT}$ ) of the power converters employing TFTs are demonstrated to be limited by their  $R_{ON}$ . At the system level, the optimum operating point of a solar cell is found to change when it is connected to the power conversion system. Due to the losses in the power conversion circuitry, net  $I_{OUT}$  can be increased by reducing  $f_{SW}$  and the switching loss. In addition, the system performance is found to be heavily affected by the process parameters. For instance, the area of the circuit can be reduced 20 times if the GrS of the TFT's are increased for the "Worst" process in Table IV. On the other hand, it is shown that even though the performance of the solar cell is improved by changing process parameters, the TFT performance can still significantly limit the system performance. Finally, it is demonstrated that high power conversion efficiencies (78 to 89%) can be achieved by using poly TFTs.

#### REFERENCES

- A. Milenković, C. Otto and E. Jovanov, "Wireless sensor networks for personal health monitoring: Issues and an implementation," *Computer Communications*, vol. 29, no. 13-14, pp. 2521-2533, 2006.

- [2] T. Wark, P. Corke, P. Sikka, L. Klingbeil, Y. Guo, C. Crossman, P. Valencia, D. Swain and G. Bishop-Hurley, "Transforming Agriculture through Pervasive Wireless Sensor Networks," *IEEE Pervasive Computing*, vol. 6, no. 2, pp. 50-57, 2007.

- [3] J. Atchison and M. Peck, "A Millimeter-Scale Lorentz-Propelled Spacecraft," in AIAA Guidance, Navigation and Control Conference and Exhibit, 2007.

- [4] N. Xu, S. Rangwala, K. Chintalapudi, D. Ganesan, A. Broad, R. Govindan and D. Estrin, "A Wireless Sensor Network For Structural Monitoring," in 2nd International Conference on Embedded Networked Sensor Systems (SenSys), 2004.

- [5] J. Paradiso and T. Starner, "Energy scavenging for mobile and wireless electronics," *IEEE Pervasive Computing*, vol. 4, no. 1, pp. 18-27, 2005.

- [6] V. Raghunathan, A. Kansal, J. Hsu, J. Friedman and M. Srivastava, "Design Considerations for Solar Energy Harvesting Wireless Embedded Systems," in Fourth International Symposium on Information Processing in Sensor Networks (IPSN), 2005.

- [7] E. S. Mungan and K. Roy, "2D Modeling and optimization of excimer laser annealed thin film polysilicon solar cells," in 37th IEEE Photovoltaic Specialists Conference (PVSC), 2011.

- [8] J. M. Hwang, P. Ho, J. E. Lewis and D. R. Campbell, "Grain boundary diffusion of aluminum in polycrystalline silicon films," *Journal of Applied Physics*, vol. 51, pp. 1576-1581, 1980.

- [9] J. L. Gray, *Private communcation*, December 2012.

- [10] E. S. Mungan, C. Lu, V. Raghunathan and K. Roy, "Modeling, design and cross-layer optimization of polysilicon solar cell based micro-scale energy harvesting systems," in *Proceedings of International Symposium* on Low Power Electronics and Design (ISLPED), 2012.

- [11] J. Li, A. Bansal and K. Roy, "Poly-Si Thin-Film Transistors: An Efficient and Low-Cost Option for Digital Operation," *IEEE Transactions on Electron Devices*, vol. 54, no. 11, pp. 2918-2929.

- [12] Subcommittee-G03.09, ASTM G173-03(2012), Standard Tables for Reference Solar Spectral Irradiances: Direct Normal and Hemispherical on 37 ° Tilted Surface, West Conshohocken, PA: ASTM International, 2012.

- [13] Synopsys Inc., Sentaurus Device Simulator, Mountain View, CA.

- [14] S. Y. Kim, S. Baytok and K. Roy, "Thin-BOX Poly-Si Thin-Film Transistors for CMOS-Compatible Analog Operations," *IEEE Transactions on Electron Devices*, vol. 58, no. 6, pp. 1687-1695, 2011.

- [15] J. Polastre, R. Szewczyk and D. Culler, "Telos: enabling ultra-low power wireless research," in *International Symposium on Information Processing in Sensor Networks (IPSN)*, 2005.

- [16] M. S. Shur, H. C. Slade, T. Ytterdal, L. Wang, Z. Xu, M. Hack, K. Aflatooni, Y. Byun, Y. Chen, M. Froggatt, A. Krishnan, P. Mei, H. Meiling, B. H. Min, A. Nathan, S. Sherman, M. Stewart and T. S., "Modeling and Scaling of a-Si:H and Poly-Si Thin Film Transistors," in MRS Proceedings, 1997.

- [17] H. Shao, C. Y. Tsui and W. H. Ki, "A micro power management system and maximum output power control for solar energy harvesting applications," in *International Symposium on Low Power Electronics* and Design (ISLPED), 2007.

- [18] M. Seeman and S. Sanders, "Analysis and Optimization of Switched-Capacitor DC-DC Converters," in *Computers in Power Electronics* (COMPEL), 2006.

- [19] S. Sambandan, Circuit Design Techniques for Non-Crystalline Semiconductors, Boca Raton, FL: CRC Press, 2012.

- [20] C. Lu, S. P. Park, V. Raghunathan and K. Roy, "Low-overhead maximum power point tracking for micro-scale solar energy harvesting systems," in VLSI Design Conference, 2012.

Elif Selin Mungan (S'05) received her B.S. degree in electronics engineering from Sabanci University, Istanbul, Turkey in 2008, her M.S. degree in electrical and computer engineering from Purdue University, West Lafayette, IN in 2010 and her PhD degree in electrical and computer engineering from Purdue University, West Lafayette, IN in 2015.

Her current research interests are silicon and non-silicon device modeling for low cost - low power flexible electronics applications such as thin

film transistors and solar cells from the device/circuit co-design point of view to address challenges at different levels of system design.

Dr. Mungan was the recipient of Sakip Sabanci Encouragement Scholarship for her academic excellence from 2005 to 2008 and the IEEE MTT Society Undergraduate Scholarship for her thesis work in 2008.

.

Chao Lu received his B.S. degree in electrical engineering from the Nankai University, Tianjin, China in 2004 and the M.S. degree in the Department of Electronic and Computer Engineering from the Hong Kong University of Science and Technology, Hong Kong, in 2007. He obtained his Ph.D. degree at Purdue University, West Lafayette in 2012. He worked as an analog IC designer in Arctic Sand Technologies Inc. and Tezzaron Semicondutor in 2013 and 2014. In 2015 he joined Southern Illinois University, Carbondale, IL, as an assistant professor.

His research interests include design of microscale energy harvesting systems, and power

management IC design for ultra low power applications.

Dr. Lu was the recipient of the Best Paper Award of the

Dr. Lu was the recipient of the Best Paper Award of the International Symposium on Low Power Electronics and Design (2007).

**Chih-Hsiang Ho** received the Ph. D. degree from Purdue University at West Lafayette, IN, USA, in 2014. He is currently working with Qualcomm as a Sr. system engineer.

Kaushik Roy (F'12) received the B.Tech. degree in electronics and electrical communications engineering from the Indian Institute of Technology, Kharagpur, India, and the Ph.D. degree from the Electrical and Computer Engineering Department, University of Illinois, Urbana-Champaign, IL, USA, in 1990.

He was with the Semiconductor Process and Design Center of Texas Instruments, Dallas, TX, USA, where he worked on FPGA architecture

development and low-power circuit design. He joined the Electrical and Computer Engineering Faculty at Purdue University, West Lafayette, IN, USA, in 1993, where he is currently Edward G. Tiedemann Jr. Distinguished Professor. His research interests include spintronics, device-circuit co-design for nanoscale Silicon and non-Silicon technologies, low-power electronics for portable computing and wireless communications, and new computing models enabled by emerging technologies. He has published more than 600 papers in refereed journals and conferences, holds 15 patents, graduated 60 Ph.D. degree students, and is co-author of two books on low power CMOS VLSI design (Wiley and McGraw Hill).

Dr. Roy received the National Science Foundation Career Development Award in 1995, IBM faculty partnership award, ATT/Lucent Foundation award, 2005 SRC Technical Excellence Award, SRC Inventors Award, Purdue College of Engineering Research Excellence Award, Humboldt Research Award in 2010, 2010 IEEE Circuits and Systems Society Technical Achievement Award, Distinguished Alumnus Award from Indian Institute of Technology (IIT), Kharagpur, Fulbright-Nehru Distinguished Chair, DoD National Security Science and Engineering Faculty Fellow (2014–2019), and several best paper awards. He was a Purdue University Faculty Scholar (1998–2003). He was a Research Visionary Board Member of Motorola Labs (2002) and held the M. K. Gandhi Distinguished Visiting faculty at Indian Institute of Technology (Bombay). He has been in the editorial board of IEEE DESIGN & TEST, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS, IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, and IEEE TRANSACTIONS ON ELECTRON DEVICES.