# Southern Illinois University Carbondale **OpenSIUC**

Conference Proceedings

Department of Electrical and Computer Engineering

5-1-2007

# A Programmable Window Comparator for Analog Online Testing

Amit Laknaur Southern Illinois University Carbondale

Rui Xiao Southern Illinois University Carbondale

Haibo Wang Southern Illinois University Carbondale, haibo@engr.siu.edu

Follow this and additional works at: http://opensiuc.lib.siu.edu/ece\_confs

Published in Laknaur, A., Xiao, R., & Wang, H. (2007). A programmable window comparator for analog online testing. 25th IEEE VLSI Test Symmposium (VTS'07), 119-124. doi: 10.1109/VTS.2007.8 ©2007 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. This material is presented to ensure timely dissemination of scholarly and technical work. Copyright and all rights therein are retained by authors or by other copyright holders. All persons copying this information are expected to adhere to the terms and constraints invoked by each author's copyright. In most cases, these works may not be reposted without the explicit permission of the copyright holder.

### Recommended Citation

Laknaur, Amit; Xiao, Rui; and Wang, Haibo, "A Programmable Window Comparator for Analog Online Testing" (2007). *Conference Proceedings*. Paper 48.

http://opensiuc.lib.siu.edu/ece confs/48

This Article is brought to you for free and open access by the Department of Electrical and Computer Engineering at OpenSIUC. It has been accepted for inclusion in Conference Proceedings by an authorized administrator of OpenSIUC. For more information, please contact <a href="mailto:nabe@lib.siu.edu">nabe@lib.siu.edu</a>.

### A Programmable Window Comparator for Analog Online Testing

Amit Laknaur, Rui Xiao, and Haibo Wang Department of Electrical and Computer Engineering Southern Illinois University, Carbondale, IL 62901

#### **Abstract**

This paper discusses the challenge of designing window comparators for analog online testing applications. A programmable window comparator with adaptive error threshold is presented. Experimental results demonstrate that improved fault detection capability is achieved by using the proposed design. Measurement results of the fabricated comparator circuit are also presented.

#### 1 Introduction

Online testing has been widely used in mission-critical applications to improve the fidelity of electronic systems. Various techniques have been developed to perform online testing for analog circuits [1, 2, 3, 4, 5, 6, 7]. Among those techniques, an useful approach is to duplicate a portion of the circuit under test and compare the outputs of the original circuit and its replication [1, 8, 9] (redundancy based approach). Analog window comparators are normally used for such purposes. An analog window comparator contains two analog inputs and a digital output. Its output switches from one logic value to the other when the difference between window comparator inputs exceeds the range of  $[-V_{\epsilon}, V_{\epsilon}]$ , where  $V_{\epsilon}$  is referred to as the window comparator error threshold.

There are three types of window comparator error thresholds, namely *constant*, *relative*, and *adaptive* error thresholds. In the first category [10, 11, 12, 13, 14, 15, 16, 17, 18], the error threshold of a window comparator is constant regardless of its input signal levels. This type of window comparators quickly lose their fault-detection capabilities when signals being monitored become small. While window comparators with relative error thresholds [14, 19] overcome such problems by making their error thresholds proportional to input signal levels, the drawback associated with such circuits is that error thresholds become too small when window comparator inputs are close to the signal ground level. Thus, small differences caused by tolerable circuit mismatches may be incorrectly identified as faults. Analog checkers with

adaptive error thresholds are presented in [19, 20, 21]. These circuits use pairs of inverters to digitize the amplified input difference. The adaptive error threshold is implemented by dynamically adjusting the impedance of the pull-up paths of the inverters according to input signal levels. Improved concurrent error detection capabilities have been reported with using these comparators.

In this paper, we demonstrate the need for programmable adaptive window comparators in online testing analog reconfigurable circuits. We also present a comparator design that can automatically adjust its threshold according to the input signal magnitude. More interestingly, the comparator's error threshold adapting scheme can be digitally programmed. This makes it possible to attune the window comparator for more effectively testing different circuits with distinctive characteristics. Experimental results demonstrate that improved fault detection capability is achieved by using the proposed design. The proposed comparator is fabricated using a  $0.18\mu$  CMOS technology. Measurement results of the fabricated comparator are also presented.

The rest of the paper is organized as follows. Section 2 reviews redundancy-based online testing techniques on analog reconfigurable platforms. It also discusses the need for programmable adaptive error threshold and introduces parameters for characterizing the comparator adaptive error threshold. Section 3 describes the proposed comparator design. Experimental results are presented in Section 4, and the paper is concluded in Section 5.

#### 2 Preliminaries

# 2.1 Analog online testing on reconfigurable hardware platforms.

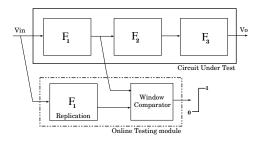

The redundancy-based online testing scheme is illustrated in Figure 1. In order to reduce testing-hardware overhead, reconfigurable hardware has been used to implement the redundant testing module. By exploiting the reconfigurability, the same hardware can be used to test different sections of the circuit [1, 8, 9, 22].

Recently Field Programmable Analog Arrays (FPAAs) have emerged as a promising platform to implement analog circuits with fault recovery capability [23]. To cost-effectively detect faults occurred in an FPAA circuit, a set

$<sup>^\</sup>dagger \text{This}$  work is partially supported by National Science Foundation under the grant No.0448357

Figure 1. Redundancy based On-line testing.

of configurable resources can be periodically programmed to replicate different sections of the circuit under test (CUT). The output of the original circuit and the replication are monitored by a window comparator to detect the occurrence of faults. By taking advantage of dynamic reconfiguration capability of modern FPAAs, testing operations can be carried out without interrupting the normal operation of the circuit. When a circuit fault is detected, FPAAs can be reconfigured to replace the fault component with unused resources. Since different sections of a circuit may have distinctive characteristics, they may require custom designed comparator error threshold in order to achieve high fault detection capability. This is elaborated in the following section.

#### 2.2 Optimal comparator error threshold

In the testing setup shown in Figure 1, the output of the original circuit and its replication should be identical in the ideal case. However, due to device mismatches and circuit parasitics, normally there is a small difference between the outputs of the two circuits even in the fault free scenario. Consequently, the error threshold of the window comparator should be selected slightly larger than this difference in order to detect faulty circuits and ignore the variations caused by the above circuit non-ideal effects. Assume the CUT is a linear circuit. For given tolerable circuit mismatches, the difference between the original and its replication (here after referred to as  $\Delta V$ ) is proportional to the magnitude of the signal under scrutiny. To more effectively detect circuit faults, relative and adaptive error thresholds are presented in [19, 20, 21, 14, 13]. Their error threshold can be written as:

$$V_{\epsilon} = k \cdot V_{sig} + V_{gb} \tag{1}$$

where k is the proportionality constant between  $V_{\epsilon}$  and original circuit output  $V_{sig}$ . And  $V_{gb}$  is the guardband as discussed in [24, 25]. As mentioned early, the window comparator is time-shared to test different sections of the circuit. To enhance fault detection capabilities, the proportionality constant k used to determine comparator error threshold may need to be attuned to the different characteristics of the sub circuits under tested. Hence, window comparators with programmable adaptive error thresholds

are preferred in online testing reconfigurable analog circuits.

#### 2.3 Programmable Adaptive threshold

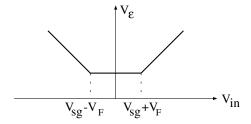

The proposed adaptive error threshold is shown in Figure 2. When its input signals are large, the window comparator uses the relative error threshold scheme. If the window comparator experiences small input signals, it switches to the constant error threshold method. By adaptively selecting error thresholds, the proposed window comparator will efficiently detect circuit faults no matter input signals being large or small.

For the convenience of discussion, we assume input signals are centered at the signal ground level  $V_{sg}$  and the maximum peak-to-peak value of the input is  $2 \cdot V_A$ , where  $V_A$  is the maximum magnitude of the signal. We refer to the region that the comparator has a constant error threshold as the *flat band region*. The voltage,  $V_F$ , at which the window comparator leaves the flat band region is called flat band voltage. The ratio of  $V_F$  to  $V_A$  is called flat band ratio and denoted by symbol  $\mathcal{R}$ . In addition, the comparator error threshold in the constant threshold region is defined as the minimum error threshold  $V_{\epsilon}^{min}.$  The slope of the error threshold curve in the relative error threshold region is k. To meet the programmability requirement discussed in Section 2.2, parameters  $\mathcal{R},\,V_{\epsilon}^{min}$  and k, which characterize the comparator threshold adapting schemes, should be digitally programmed. A comparator design that implements the proposed programmable adaptive error threshold is discussed in the next section.

Figure 2. Adaptive threshold.

#### 3 Proposed Window Comparator

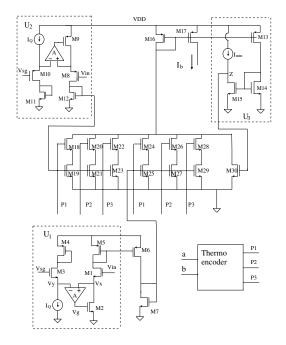

The proposed design consists of an adaptive biasing circuit and a checker circuit whose error threshold can be programmed through its biasing current and device ratios.

#### 3.1 Checker circuit

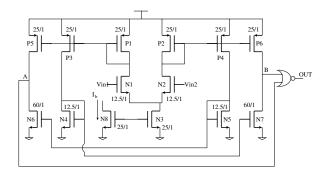

The checker circuit, as shown in Figure 3, is comprised of a differential input pair and four current mirrors. Transistors  $N_1$  and  $N_2$  constitute the differential pair. PMOS devices  $P_1 \sim P_6$ , which have the same size, implement two sets of PMOS current mirrors. Transistors  $N_4$  and

$N_7,\,N_5$  and  $N_6$ , realize two NMOS current mirrors with a current gain of m (the size of  $N_6$  and  $N_7$  is m times larger than that of  $N_4$  and  $N_5$ ). Assume the current flowing through  $N_3$  is  $I_b$ . When both checker inputs are at the same level,  $N_1,\,N_2,\,N_4,\,N_5$ , and  $P_1\sim P6$  are in their saturation regions; and all the currents flowing through these transistors are  $\frac{I_b}{2}$ .  $N_6$  and  $N_7$ , working in their linear regions, pull voltages at nodes A and B close to ground, driving the checker output to logic I.

Figure 3. Proposed comparator sub-circuit.

Without losing generalities, assume checker input  $V_{in1}$  becomes larger than input  $V_{in2}$ . Consequently, currents flowing through  $N_1$  and  $N_2$  become  $\frac{I_b}{2}+i$  and  $\frac{I_b}{2}-i$ , where i is the current variation caused by the input difference. When  $\frac{I_b}{2}+i>m\cdot(\frac{I_b}{2}-i)$ , the voltage at node A is pushed close to  $V_{DD}$  and, hence, the checker output switches to logic 0. Assuming that  $I_{DS}$  and  $V_{GS}$  relations of  $N_1$  and  $N_2$  follow the perfect square-law, the checker error threshold can be derived as:

$$V_{\epsilon} = \sqrt{\frac{2 \cdot I_b}{\mu_n \cdot C_{ox} \cdot (W/L)_{N1,2}}} \cdot \sqrt{1 - \sqrt{1 - (\frac{m-1}{m+1})^2}}$$

(2)

where  $\mu_n$  is the carrier mobility;  $C_{ox}$  is the transistor gate unit capacitance; and  $(W/L)_{N1,2}$  is the size of  $N_1$  and  $N_2$ .

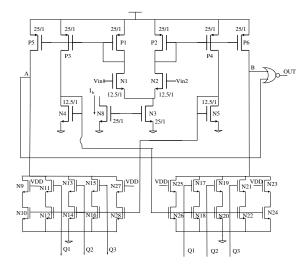

The above equation shows that the comparator threshold can be adjusted by varying the value of m. A modified comparator circuit with programmable m values is shown in Figure 4. In the modified design, programmable current mirror (PCM) circuits replace the simple current mirrors  $(N_4 \sim N_7)$  used in the original design. The output branch of a PCM circuit consists of five current sink paths. Three of them can be turned on or off depending on digital signals  $Q_1, Q_2, Q_3$ , which represent a 3-bit thermometer code. The other two paths are always on to keep the minimum value of m as 2. A binary to thermometer code encoder converts two digital programming inputs to thermometer code  $Q_1, Q_2, Q_3$ . Assume all the transistors in PCM circuits have the same size, m can be programmed from 2 to 5. Consequently, the comparator error threshold can be scaled by factors ranging from 0.24 to 0.5.

Figure 4. Modified comparator sub-circuit.

#### 3.2 Programmable adaptive biasing circuit

Equation (2) also indicates that the checker error threshold is proportional to the square root of its biasing current. To achieve the adaptive error threshold shown in Figure 1, the biasing current should be proportional to the square of the input magnitude when the input is in the relative error threshold region. When the input is in the constant threshold region, the biasing current should be a constant. The proposed biasing circuit is given in Figure 5. It includes three current-generating blocks, labeled as  $U_1$ ,  $U_2$ , and  $U_3$ . Transistors  $M_{16}$ - $M_{30}$  generate the output biasing current according to the following equation.

$$I_b = \begin{cases} I_{min} & \text{for } V_{sg} - V_f < V_{in} < V_{sg} + V_f \\ w \cdot I_p & \text{for } V_{in} < V_{sg} - V_f \\ w \cdot I_n & \text{for } V_{in} > V_{sg} + V_f \end{cases}$$

$$(3)$$

where  $I_p$  and  $I_n$  are output currents of  $U_1$  and  $U_2$ , respectively. w is the scaling factor that is controlled by programmable inputs a and b. When checker input  $V_{in}$  is within the *flat band region*,  $w \cdot I_p$  (or  $w \cdot I_n$ ) are smaller than  $I_{min}$ . In this case, transistor  $M_{15}$  will drain current to make sure  $I_b = I_{min}$ . Hence, the checker has a constant error threshold.

If  $V_{in}$  is greater than signal ground level  $V_{sg}$ ,  $M_8$  in  $U_2$  is off and  $M_1$  in  $U_1$  conducts current. After  $V_{in}$  leaves the flat band region,  $w \cdot I_n$  becomes larger than  $I_{min}$ . Subsequently,  $M_{15}$  is off and  $I_b = w \cdot I_n$ . In the design,  $I_Q$  is very small and all the transistors in  $U_1$  are in their saturation regions. Thus,  $I_b$ , which is the same as  $I_{DS1}$ , can be derived as:

$$I_{b} = \frac{\mu_{n} \cdot C_{ox}}{2} \cdot \frac{w \cdot (W/L)_{M1}}{1 + \frac{1}{A} \cdot \sqrt{\frac{(W/L)_{M1}}{(W/L)_{M2}}}} \cdot (V_{in} - V_{sg} - \frac{V_{t}}{A})^{2}$$

(4)

Figure 5. Proposed adaptive biasing circuit.

where  $V_t$  is the threshold of MOS devices and A is the gain of the amplifier used in  $U_1$ . Ignoring the term of  $\frac{V_t}{A}$  in the above equation, the biasing current becomes proportional to the square of the input magnitude  $(V_{in}-V_{sg})$ . As a result, the checker has relative error thresholds. When  $V_{in}$  is smaller than  $V_{sg}$  and out of the flat band region, the biasing current  $I_b$ , which will be generated by  $U_2$ , is also proportional to the square of the input signal magnitude to implement relative error thresholds.

The programmability of the biasing circuit is realized by controlling the scaling factor w. A binary to thermometer code encoder circuit converts 2-bit programming inputs a and b to 3-bit thermometer code P1,P2, P3, which control the status of the current sinking paths in the PCM circuits. When a=0 and b=0, all three programmable current sinking paths are off. The biasing current becomes independent of  $U_1$  and  $U_2$  outputs. Thus the comparator circuit has a constant error threshold. Note that varying w values changes both comparator threshold gain and flat band ratio, because a large w value will cause  $w \cdot I_n$ , or  $w \cdot I_p$  exceeds  $I_{min}$  early, and resulting a small flat band ratio.

#### 4 Experiment Results

#### 4.1 Simulation results

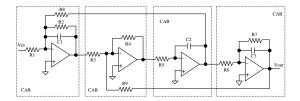

Circuit simulation has been conducted to study how the optimal comparator error thresholds should be adjusted for different sections of the CUT. An experiment circuit used in this study is a third-order chebyshev low pass fil-

ter circuit, whose schematic is shown in Figure 6. The passband of the filter is 10kHz. We also partition the circuit into four different sections, and assume that a reconfigurable testing module sequentially tests the partitioned sections.

Figure 6. Leapfrog filter.

To determine the optimal comparator error threshold for a given circuit section, circuit simulation (e.g. Monte Carlo simulation) can be performed to find the maximum difference between the outputs of the original circuit and its duplication due to parasitics and circuit mismatches. For the reason of simplicity we assume each component in the circuit can vary by 0.5% of its ideal value due to process imperfections. Then, we identify the worst-case component values that lead to the maximum signal difference. To reduce simulation time, we use an amplifier macromodel in the simulation. The key parameters assigned to the amplifier model are summarised in Table 1.

Table 1. Opamp macromodel parameters.

| Opamp parameters            | Values            |

|-----------------------------|-------------------|

| Low frequency gain          | 80dB              |

| Unit-gain frequency         | 10MHz             |

| Common mode rejection ratio | 70dB              |

| Input offset voltage        | 4mV               |

| Slew Rate                   | $20V/\mu s$       |

| Settling time (0.1%)        | $0.5 \mu s$       |

| Power supply                | 3.3V              |

| Output swing range          | $0.18V \sim 3.1V$ |

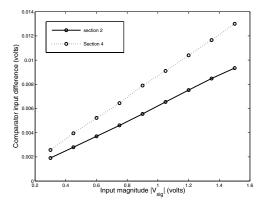

With allowed component value variations, the maximum signal difference  $\Delta V$ s for the second and the fourth sections of the filter circuit are plotted in Figure 7. In the simulation, we vary the magnitude of the filter input such that the signal magnitude at the output of the sub circuits (sections) are also changed. Figure 7 clearly shows that the signal difference  $\Delta V$ s are proportional to the magnitude of the signals under scrutiny. This justifies the need for the adaptive error threshold scheme. The plot also shows that the relations between  $\Delta V$  and the magnitudes of the signal under scrutiny for the second and the fourth sections are different. It explains the need for programmability in window comparator circuits.

With using the leapfrog filter as an example circuit, we also compared the fault detection capabilities when using the proposed comparator and a conventional one with constant error threshold. The constant error threshold value is

Figure 7. Difference between the outputs of the CUT and its replication.

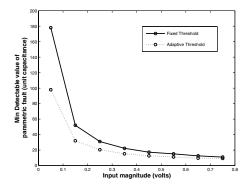

selected according to the maximum  $\Delta V$  value. The proposed comparator used in the experiment has an adaptive error threshold that fits the  $\Delta V$  behavior for the CUT. In the experiment, we inject parametric faults at component  $C_1$  in the first section of the filter circuit. Figure 8 shows how the detectable faults vary with different filter input levels. The reported detectable faults are described by their variations from the normal component value, which is 255 unit capacitances. Thus a smaller value indicates a less severe fault. It shows fault detection capability degrades for both the comparators when the filter circuit has a smaller input. This is mainly due to adding the guardband component in the error threshold. Nevertheless, the experiment results clearly show an improved fault detection capability is achieved by using the proposed comparator.

Figure 8. Minimum detectable fault at  $C_1$  with different filter input levels.

## **4.2** Measurement results of the fabricated comparator

The proposed comparator has been implemented using a  $0.18\mu$  CMOS technology. Transistor sizes used in the checker circuit are given in Figure 3. Single-stage differ-

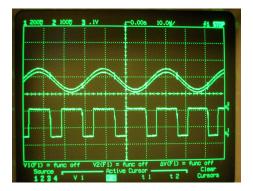

ential amplifiers [26] are used in the adaptive biasing circuit. The design requires a single 3.3V power supply and the signal ground level is 1.65V. Figure 9 shows a testing result of the fabricated chip. The inputs of the checker are two sinusoidal signals  $V_{in1}$  and  $V_{in2}$  with the same magnitude, frequency, and phase.  $V_{in1}$  is centered at the signal ground level, while  $V_{in2}$  is shifted down by 160 mV. Input  $V_{in1}$  is also connected to the biasing circuit (as is Vin shown in Figure 5) to control the biasing current. The square-like wave in Figure 9 shows that this difference is detected by the checker (checker output is logic 0) when the signal values are close to the signal ground level. When the inputs are close to their peak values, the same difference is ignored by the checker due to its increased error threshold.

Figure 9. Captured oscilloscope display.

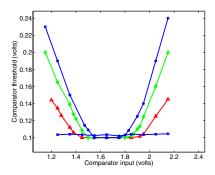

The programmability of the proposed design is also verified by our testing results. Figure 10 shows measured comparator thresholds at different input levels. The four curves in the figure correspond to the realized comparator error thresholds with different digital values applied to the programmable inputs a and b of the biasing circuit (depicted in Figure 5). When both a and b are logic 0, a constant error threshold is realized seen as a flat straight line over the entire input range. With other digital ab values, the proposed adaptive error threshold scheme is observed.

### 5 Concluding Remarks

This paper discusses the optimal error threshold for window comparators used in analog online testing. A window comparator with programmable adaptive error threshold is presented. Experiment results demonstrated that improved fault detection capabilities can be achieved by using the proposed comparator. The proposed comparator has been designed and fabricated using a  $0.18\mu$  CMOS technology. Measurement results of the fabricated chip are also presented.

Although the proposed design is more complex compared to previous designs, its programmability will allow a single comparator to be time-shared to test different sec-

Figure 10. Programmable adaptive error thresholds.

tions of the CUT with a better fault detection capability. The comparator itself can also be tested using simple built-in-self-testing (BIST) circuits. A simple approach is to feed the comparator inputs with ramp signals and use counters to monitor when the comparator output switches. Combining this BIST feature, the comparator will be suitable for implementing online testing circuits on analog reconfigurable platforms.

#### References

- [1] J. L. Huertas and A. Rueda and D. Vazquez, "Testable Switched-Capacitor Filters," *Journal of Solid-State Circuits*, vol. 28, no. 7, pp. 719–724, 1993.

- [2] J. Velasco-Medina and I. Rayaneand M. Nicolaidis, "On-Line BIST for Testing Analog Circuits," in *Proc. ICCD*, pp. 330–332, 1999.

- [3] M. Negreiros and L. Carro and A. A. Susin, "A Statistical Sampler for a New On-Line Analog Test Method," *Journal* of Electronic Testing, vol. 19, pp. 585–595, 2003.

- [4] O.K.Abu-Shahla and I.M.Bell, "An On-line Self-testing Switched -current Integrator," in *Proc. IEEE International Test Conference*, pp. 463–470, 1997.

- [5] A. Chatterjee, "Checksum-Based Concurrent Error Detection in Linear Analog Systems with Second and Higher Order Stages," in *Proc. VLSI Test Symp.*, pp. 286–291, 1992.

- [6] J. Velasco-Medina and M. Nicolaidis and M. Lubaszewski, "An Approach to the On-Line testing of Operational Amplifiers," in *Proc. 7th Asian Test Symposium*, pp. 290–295, 1998

- [7] B. Vinnakota and R. Harjani, "The Design of Analog Self-Checking Circuits," in *Proc. Int. Conf. VLSI Design*, pp. 67–70, 1994.

- [8] D. Vazquez and A. Rueda and J. L. Huertas, "A Solution for the On-Line Test of Analog Ladder Filters," in *Proc. VLSI Test Symp.*, pp. 48–53, 1995.

- [9] D. Vazquez and A. Rueda and J. L. Huertas and E. Peralias, "A High-Q Bandpass Fully Differential SC Filter with Enhanced Testability," *Journal of Solid-State Circuits*, vol. 33, no. 7, pp. 976–986, 1998.

- [10] J. E. Franca, "Analogue-Digital Window Comparator with Highly Flexible Programmability," *IEE Electronics Letters*, pp. 2063–2064, 1991.

- [11] Y. Zhang and M. W.T.Wong, "Self-Testable Full Range Window Comparator," in *Proc. Region 10 TENCON 2004*, vol. 4, pp. 262–265, 2004.

- [12] M. Lubaszewski and V. Kolarik and S. Mir and C. Nielsen and B. Courtois, "Mixed-Signal Circuits and Boards for High Safety Applications," in *Proc. European Design and Test Conference*, pp. 34–39, 1995.

- [13] V. Kolarik and M. Lubaszewski and B. Courtois, "Designing Self-Exercising Analogue Checkers," in *Proc. VLSI Test Symposium*, pp. 252–257, 1994.

- [14] V. Kolarik and S. Mir and M. Lubaszewski and B. Courtois, "Analog Checkers with Absolute and Relative Tolerances," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 14, pp. 607–612, 1995.

- [15] D. D. Venuto and M. J. Ohletz and B. Ricco, "Testing of analogue circuits via (standard) digital gates," in *Proc. Intl. Symp. on Quality Electronic Design*, pp. 112–119, 2002.

- [16] D. D. Venuto and M. J. Ohletz and B. Ricco, "Digital Window Comparator for mixed-signal IC's design for testability," *Journal of Electronic Testing: Theory and Applications*, vol. 18, no. 2, pp. 121–128, 2002.

- [17] D. D. Venuto and M. J. Ohletz and B. Ricco, "Automatic Repositioning Technique for Digital Cell Based Window Comparators and Implementation within Mixed-Signal DfT Schemes," in *Proc. Intl. Symp. on Quality Electronic Design*, pp. 431–437, 2003.

- [18] D. D. Venuto and M. J. Ohletz, "On-Chip Test for Mixed-Signal ASICs using Two-Mode Comparators with Biasprogrammable reference voltages," *J. of Electronic Test*ing: Theory and Applications, vol. 17, pp. 243–253, 2001.

- [19] H. Stratigopoulos and Y. Makris, "An Analog Checker with Dynamically Adjustable Error Threshold for Fully Differential Circuits," in *Proc. VLSI Test Symposium*, pp. 209–214, 2003.

- [20] H. Stratigopoulos and Y. Makris, "An Analog Checker with Input-Relative Tolerance for Duplicate signals," *Jour*nal of Electronic Testing: theory and applications, vol. 20, pp. 479–488, 2003.

- [21] H. Stratigopoulos and Y. Makris, "An Adaptive Checker for the Fully Differential Analog Code," *IEEE J. Solid-State Circuits*, vol. 41, no. 6, pp. 1421–1429, 2006.

- [22] H. Wang and S. Kulkarni and S. Tragoudas, "Circuit Techniuqes for Field Programmable Analog Array On-Line Testing," in *Proc. 10th International Mixed-Signal Testing Workshop*, pp. 237–244, 2004.

- [23] Amit Laknaur and Haibo Wang, "A Methodology to Perform Online Self-Testing for Field-Programmable Analog Array Circuits," *IEEE Trans. on Instrumentation and Measurement*, vol. 54, no. 5, pp. 1751–1760, 2005.

- [24] P. Mullenix, "The Capability of Capability Indics with an Application to Guardbanding in a Test Environment," in Proc. International Test Conference, pp. 907–915, 1990.

- [25] R. H. Williams and C. F. Hawkins, "The Economics of Guardband Placement," in *Proc. International Test Con*ference, pp. 218–225, 1993.

- [26] P. Allen and D. Holberg, CMOS Analog Circuit Design. Oxford University Press, 2002.